富士通研究所は4月24日、ディープラーニングの学習処理に用いるデータのビット幅を削減することで、ニューラルネットワーク構造や学習方式を変えずに学習用ハードウェアの電力効率を向上させる回路技術を開発したと発表した。

GPUの性能向上により、ディープラーニングの学習プロセスは劇的な進化を遂げたが、学習用データの増大は、ストレージ量の増大につながるほか、近年ではエッジノードでの学習を行いたいというニーズも出てきており、より消費電力を抑えつつ、高い学習効率を実現する技術が求められるようになってきている。

従来、ディープラーニングの学習プロセスでは、32ビットの浮動小数点演算が行われてきた。すでに推論プロセスでは、16ビットの浮動小数点演算(FP16)や8ビットの整数演算(INT8)を用いることで演算量を削減し、電力効率を高めることができることがわかってきたが、学習の過程においては、演算途中で必要とする精度が不足し、学習ができなくなったり、ディープラーニングの認識性能が劣化するという課題があった。

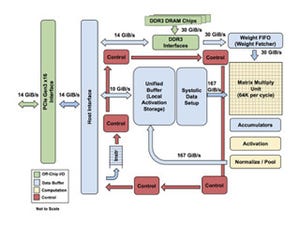

そこで研究グループは今回、整数演算を基にして、ディープラーニングの学習プロセスに特化してビット幅を削減した独自の数値表現と多層ニューラルネットワークの層ごとに演算中のデータを随時解析しながら演算精度を保つように小数点の位置を自動的に制御する演算アルゴリズムにより、ディープラーニングの学習過程において、演算器のビット幅や学習結果を記録するメモリのビット幅を削減し、電力効率を向上できる回路技術を開発。演算コアに、「演算中のデータを解析するブロック」、「解析したデータの分布を保存するデータベース」、「演算の設定を保持するブロック」を有し、データ解析ブロックにてディープラーニングの学習中に演算器の出力データをリアルタイムに解析を行い、データ分布を表す統計情報としてデータベースに保存。その分布から、ディープラーニングの学習精度を向上させるために十分な演算精度を保つことができるように学習に最適な設定をして演算を進めることを可能としたという。

具体的には、32ビットの浮動小数点演算から8ビットの整数演算にビット幅を削減することで、メモリや演算器の消費電力を約75%削減できるようになるという。実際に、同技術を活用してLaNetとMNISTのデータセットを用いて学習を行ったところ、32ビット浮動小数点演算での学習結果(認識率)98.90%に対し、16ビットで98.89%、8ビットで98.31%の認識率で学習できることを確認したとする。

なお富士通研究所では、今回開発した技術を富士通のAI技術「Human Centric AI Zinrai(ジンライ)」の1つとして2018年度の実用化を目指していくとしている。また、今回開発された技術の詳細は、4月24日から26日にかけて開催される「xSIG 2017(The 1st. cross-disciplinary Workshop on Computing Systems, Infrastructures, and Programming)」にて発表される予定だという。