既報の通り、ARMは「DynamIQ」と呼ばれる新しい技術を北京で発表した(Photo01~02)。

|

|

|

|

Photo01:Nandan Nayampally氏(VP of Marketing, CPU Group)。氏が手を掛けてるものが"DynamIQ"ネオン |

Photo02:そのネオンが点灯するとこんな感じ。ちなみに手前はIan Smythe氏の後頭部 |

これに関しては、発表者であるNandan Nayampally氏のBlogエントリーも上がっているのだが、そもそもの説明ページが敢えて誤解を招きやすくしている(とまで言うと語弊があるが)感があり、ちょっと判りにくい。そこで、発表内容をまず簡単に御紹介してから、もうすこし中身をきちんと説明したい。

ARMは過去22年掛けて500億個のチップを2013年までに出荷したが、その後の4年間で同じく500億個を出荷しており、2021年までには1000億個のチップを出荷する、としている。この、次の100億個のチップに向けて新しいエコシステムの確立が求められている、というのが同社の認識だ(Photo04)。

|

|

|

|

Photo03:もちろんARMそのものが出荷したのではなく、ARMのパートナー企業が出荷したものとなる |

Photo04:ここでエコシステムが指すものは広範にわたるわけなので、何か1つやれば済むというものでもないことに注意が必要だ |

さてその中で今回同社がフォーカスしたのはCortex-A向けのマーケットである。このマーケット、2009年から比較するとすでに性能は100倍になっており、しかもエッジデバイスからクラウドまでに対応することになっている(Photo05)。8年で100倍の性能改善だから、今後2020年までにどこまで性能が上がることが求められているか、というとこちらも数十倍が期待されているわけだ(Photo06)。

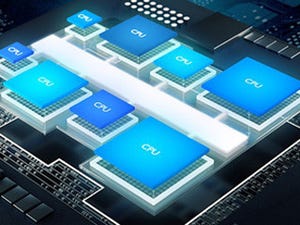

ということでDynamIQである。これはなにかというと、新しいCPUクラスタの定義となる(Photo07)。この結果として、例えばAIの学習のような、より演算性能が必要となる用途向けに現在の50倍ほどのパフォーマンスを提供できるようになる、あるいは専用アクセラレータを現在よりも10倍早いレスポンスタイムで利用できるようになる、という話になる(Photo08)。

|

|

|

|

Photo07:big.LITTLEとの最大の違いは、性能の異なるCortex-Aコアを1つのクラスタとしてまとめ、かつそのクラスタの中でスケジューリングができることになる |

Photo08:ちなみにここにあるように「今後3~5年の間に出てくるCPUを使うことで」という話であって、今のCortex-Aコアが50倍の性能になる訳ではもちろんない |

またこのDynamIQは当然機能安全にも対応しており、ASIL-Dに対応できる用意があるとする(Photo09)。

|

|

|

Photo09:実は直接的な意味で言えば、ISO26262 ASIL-Dが要求する膨大なドキュメントをきちんと出します、という以上の意味はなかったりする。ここに上がった3つの項目は、DynamIQを利用することで「結果として得られる」ものであり、DynamIQに何か機能安全向けの機能が入るわけではない |

従来技術とDynamIQの比較がこちら(Photo10)であるが、基本的にDynamIQは既存のbig.LITTLEと互換性がある上、さらに柔軟性がある、としている。