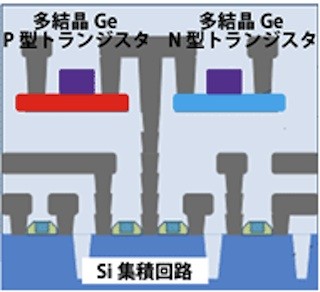

ドレスデン工科大学とナノエレクトロニクス材料ラボ(NaMlab)の研究チームは、ゲルマニウム半導体を用いた高性能トランジスタを作製した。シリコントランジスタと比べて低電圧での高速動作が可能となっている。

また、ゲート電極に印加する電圧を変えることによって、半導体のp型/n型の切り替えができるようにした。これにより、電子回路を構成するトランジスタの個数を減らせる可能性がある。研究論文は、米国化学会のナノテク専門誌「ACS Nano」に掲載された。

ゲルマニウムのバンドギャップは約0.66eV(電子ボルト)であり、バンドギャップ1.2eV程度のシリコンと比べて低い。このようにバンドギャップの小さい半導体を用いてトランジスタを作ると、チャネル部での電子移動度をシリコンと比べて高速にできることが知られている。ただし、低バンドギャップであることは、トランジスタのオフ状態でのリーク電流の原因にもなるため、待機時消費電力が増加してしまうという問題があった。

今回の研究では、この問題を解消するため、ゲルマニウムナノワイヤを用いたトランジスタのゲート部に、2つの独立したゲート電極を設けるという手法をとった。このようなデバイス構造にすることでショットキー障壁が形成され、リーク電流を防ぐためのエネルギー障壁をチャネル部に導入することができるという。

付加されたゲートは、不純物のドーピング処理などを行わなくても、一方のゲート電極にかかる電圧を制御するだけで半導体のp型/n型の極性を切り替えることができるという特徴を持っている。この性質は、現行のCMOSトランジスタに比べて電子回路に必要なトランジスタの個数を減らしたり、一つの回路にたくさんの機能を持たせたりするといったことに利用できると考えられる。

また、リーク電流を抑えるために複数のゲートを設けるという今回の手法は、ゲルマニウムだけでなく、他の材料を用いた電界効果トランジスタに対しても有効であるという。

研究リーダーのWalter Weber氏は、「(ゲルマニウムトランジスタの)低電圧動作とオフ状態でのリーク電流低減を初めて同時に実現することができた。新しい低消費電力回路を実現するための重要な成果だ」とコメントしている。