AMDは1月5日(米国時間)、同社の次世代GPUアーキテクチャ「Vega」の概要を公開した。

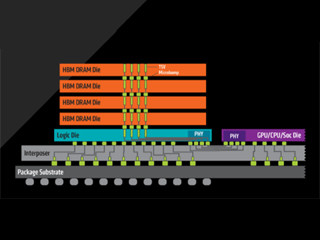

同アーキテクチャは、HBM2テクノロジーを採用。これにより、前世代のHBM比でピン当たりの帯域幅を倍増させたほか、GDDR5メモリのフットプリントの半分以下のサイズで、より大きな容量を搭載することを可能とする。また、最大512TBの仮想アドレス空間で、さまざまな種類のメモリを動作させることが可能だという。

さらに、次世代ジオメトリパイプラインにより、従来のRadeonアーキテクチャ比で200%以上のクロックスループットを提供するほか、インテリジェントなワークロード分配装置によるロードバランシングの改善により、一貫したパフォーマンスを実現するとしている。

加えて、フレキシブル・コンピューティングユニット上に構築された次世代コンピューティングエンジンは、クロックサイクルごとに8ビット/16ビット/32ビット/64ビットの各処理をネイティブに処理することが可能なほか、従来世代よりも高い周波数で動作しつつ、さまざまなデータ型をサポートするため、ワークロード全体での高い汎用性を提供するという。

このほか、Vegaピクセルエンジンは、パフォーマンスと電力効率を向上させるために設計された描画ストリーム・ビニング・ラスタライザを採用。これにより、スマートなオンチップビンキャッシュの使用と最終シーンでは見えないピクセルの早期カリング(除去)を用いることで、ピクセルの「フェッチ1回、シェード1回」を行うことを可能とした。さらに、オンボードL2キャッシュのクライアントになるため、グラフィックスワークロードのオーバーヘッドを削減し、頻繁な読み取り後書き込み操作を実行することもできるようになるとしている。