|

|

|

Lattice Semiconductorアジアパシフィック地域 事業開発担当シニアマネージャーである陳英仁(インジェン・チェン)氏 |

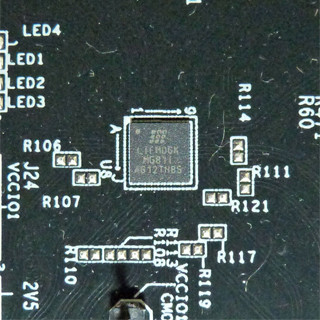

Lattice Semiconductorは、12月12日に高エネルギー効率を実現したMHC(Mobile Heterogeneous Computing)ソリューションとして、新たなFPGA「iCE40 UltraPlus」を発表を行い、12月20日に同社アジアパシフィック地域 事業開発担当シニアマネージャーである陳英仁(インジェン・チェン)氏が日本のメディア向けに、同シリーズの説明を行った。

FPGAというと、大手のXilinxやAltera(Intelが買収)は、主に通信基地局の分野を中心に、大規模な演算能力が求められる分野で市場を拡大しつつある。しかしLatticeは近年、iCE40 UltraPlusと同じiCE40ファミリとなるiCE40 UltraやiCE40 UltraLiteといった製品群を中心にモバイル分野などでの活用を模索してきており、iCE40 UltraPlusも、その流れに沿って開発されたものとなる。

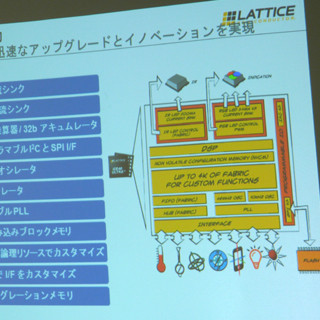

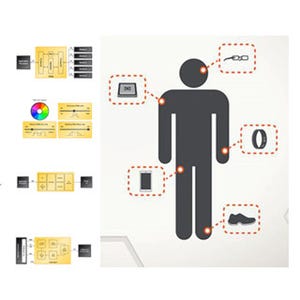

こうした取り組みは、現在、同社が掲げる「常時オン、常時待ち受け、常時接続」といった目標に基づいたものとなる。当然、注力する分野もコンシューマやIoTのエッジノードといった分野となり、iCE40UltraPlusもそうした分野のニーズや技術トレンドを取り込む形で製品化された。例えば、こうした分野では軽薄短小ながら高機能化、という2つの背反する技術要求が突きつけられ、当然のことながら、プリント基板のサイズは小型化とバッテリの長寿命化が求められつつも、多数のセンサが搭載され、常時、そこで生み出されたデータを処理する必要性が生じることとなる。「プリント基板のサイズに制約が出てくると、多くの信号を受信しつつ、小型化を実現する必要性がでてくる。そこにFPGAの柔軟性というメリットが活きてくる」(チェン氏)とのことで、アプリケーションプロセッサやマイコンとセンサなどの間を取り持つインテリジェンスを持ったI/Oハブとしての役割をiE40 UltraPlusでは担うことが第一のターゲットとなるという。

実は同社は、2016年5月にモバイル機器向けブリッジングデバイス「Lattice CrossLink」を発表済みで、搭載されるLUT(Look Up Table)数もCrossLinkのほうがiCE40 UltraPlusよりも多かったりする(CrossLinkは5936LUT、iCE40 UltraPlusは最大5280LUT)。とはいえ、1.1MビットのSRAMや8個のDSPブロック、インスタントオン用NVCM(Non-Volatile Configuration Memory)などは搭載されておらず、逆に言えば、これらを活用することで、アプリケーションプロセッサやマイコンをスリープ状態に保ちながら、スマートウォッチのディスプレイ表示や音声に対するビームフォーミング処理、ノイズ抑制、フレーズ検出、センサデータのキャプチャ、集約、暗号化、バッファリング、プリプロセスといったことを可能とし、より重い処理が必要なときだけ、プロセッサを立ち上げ、システム全体の電力消費を抑える、といったことができるようになる。

|

|

|

|

|

|

|

iCE40 UltraPlusの概要。アプリケーションプロセッサやマイコンの前段に配置され、基本的な処理を担当することで、手軽にIoTのエッジノードでプロセッシングを行うことを可能とするというのがコンセプトの1つ |

|

また、「1MビットのSRAMを利用してもスタティック消費電力は75μA未満に抑えることが可能」(同)としており、マイコンやアプリケーションプロセッサを常時駆動させるよりも、バッテリの長寿命化をはかれることを強調するほか、「用途としてはSRAMを新たに搭載したこともあり、新たな分野の開拓が期待される」とも説明しており、これまで入りきれなかった小型民生分野での採用を目指すとする。

|

|

|

同社が想定しているターゲット分野。I/Oハブ用途だと、5K LUTもいらないのでは、という話をしたところ、将来的にはIoTの通信で必要となる暗号IPを提供したり、といったことも考えており、実はそれくらいは必要となるという判断をしているとのことであった |

ちなみに、iCE40 UltraPlusはTSMCの40nmプロセスを採用して製造されているほか、アーキテクチャ的にも基本的にはiCE40ファミリに基づくものとなっており、今後、プロセスの微細化を進めることで、顧客ニーズの強化につなげたいとしていた。また、開発ツールとしては、ほかのiCE40ファミリ同様、「iCEcube2」で対応しているという。