|

|

|

Exascale以降のデバイスについて講演するコロンビア大のTheis教授 |

CMOSデバイスの微細化は限界に近づきつつあるが、デバイスの研究者は、より高性能のデバイスを作ることを諦めたわけではない。SC16において、コロンビア大学のナノ・イニシアティブのディレクタであるThomas N.Theis教授が、Beyond Exacaleの時代の新デバイスの研究開発状況について講演を行った。

Exascaleまでは、現在のCMOSの改良で到達できる。しかし、その先はCMOSではない新デバイスが必要になるという。

次の図にみられるように、CMOSロジックのスイッチエネルギーは指数関数で減少してきた。しかし、1990年代から、電源電圧Vの低減が緩やかになり、スイッチエネルギーの低減もスローダウンしている。

|

|

|

論理回路のスイッチエネルギーは順調に低減してが、1990年代に入って電源電圧の低下が緩やかになるにつれて、スイッチエネルギーの低減もゆっくりになってしまった (このレポートのすべての図は、SC16でのTheis教授の講演スライドを撮影したもの) |

MOSトランジスタはソース側のキャリアを流す量を、ゲートの電位でコントロールするデバイスであるので、ON/OFFには1V程度の電圧を必要とする。

キャリアは熱エネルギーによるエネルギー分布を持っており、Vgを上げてもより大きなエネルギーを持つキャリアはバリアを越えて流れてしまう。このスレッショルド電圧以下の領域でリーク電流が1/10になるゲート電圧を「Sub-threashold Slope」と言う。値が小さい方が傾きが急峻でスイッチ特性が良い。

電源電圧は、すでに1Vを下回っており、電源電圧の低下の余地はほとんど残っていない。したがって、スイッチエネルギーの低減の余地もあまり残っていない。

|

|

|

MOSFETはゲート電位でバリアの高さを変えて、流れる電流をコントロールする。スレッショルド電圧以下の領域でリーク電流を1/10にするゲート電圧の変化をSub-threashold Slopeと言う。値が小さい方がスイッチ特性が良い |

次の図は、SRAMのメモリセルの面積(青●、左のスケール)とコンタクト付きのゲートpoly-Si(■)と第1層のメタル配線(▲)のピッチ(右側のスケール)といった微細化を代表するパラメタの年次推移をプロットしたものである。まだ、微細化は続いているものの、その傾きは、徐々に緩やかになっており、微細化のペースがスローダウンしていることを示している。

この10年を振り返ってみると、スイッチエネルギーの低減がゆっくりになってしまったので、プロセサメーカーは電力と電力密度を現実的に冷却できる範囲に抑えるために、クロック周波数の向上を抑え、コア数の増加のペースも抑えてきた。

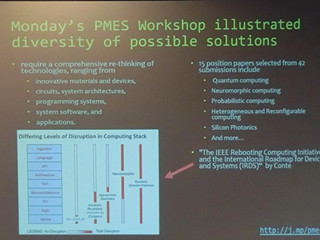

この停滞した状態から抜け出すために、MOSFETとは根本的に異なるメカニズムでスイッチするデバイス、フォンノイマンとは根本的に異なるアーキテクチャの探索を開始したという。そして、2005年に主要な半導体メーカーのIBM、Intel、Micron、TIを集めて「Nanoelectroics Research Initiative(NRI)」というコンソーシアムを立ち上げ、「NSF(National Science Foundation)」や「NIST(National Institute of Standards and Technology)」からの協力も受けて、大学の研究に資金を投入する仕組みを作った。

そして、2013年からはCMOSを超えるデバイスの探索にフォーカスし、「STARnet」と名前を替え、半導体各社とDARPAの資金も受けて6つの研究センターを立ち上げた。

研究対象のデバイスがどの程度のポテンシャルを持っているのか、CMOSと比較してメリットがあるかを判定するために、NRI-STARnetはデバイス性能のベンチマークを行っている。このために、コンパクトなデバイスモデルも開発した。

これらのモデルを使った2015年のベンチマークの結果を次の図に示す。横軸が遅延で、縦軸がエネルギーであり、左下に近いデバイスが遅延-エネルギー積が小さい。

この図ではトンネルFETのグループが一番左下にあり、磁気電気効果を使う素子と強誘電効果を使う素子がそれに続き、スピントルクを使う素子が一番遠い領域に置かれている。

なお、このベンチマークでは、それぞれのデバイスで32bit加算器を作った場合の消費エネルギーと遅延時間を評価している。

このベンチマークでは、Exascale以降の素子という明確な勝者は見つかっていないが、CMOS HPと書かれた高性能CMOSと同程度の性能の候補はいくつか見つけることができた。

まだ、次々と新しい構造のデバイスが出てきており、今後も出てくるものと思われ、CMOSを超えるデバイスが見つかる可能性もある。

2015年のベンチマークでは、新デバイスの中ではトンネルFET(TFET)がベストで、CMOSと同程度のポテンシャルを持っている。MOSFETはゲート電位でバリアの高さを上げ下げして電流をコントロールしているが、TFETはバリアの厚みを変えて、トンネル効果で通り抜けるキャリア量を変化させて、電流を変化させている。

最初に、1989年にゲートによるトンネル効果の制御が報告され、2005年にはサブスレッショルドスロープ(Sub-threshold Slope:SS)が60mV/decadeという値が報告された。これはMOSFETの90mV/decadeの2/3以下と急峻である。

しかし、TFETは流せる電流が少なく高速のスイッチが作れない。電流を大きくしようとするとSSが大きくなってMOSFETと変わらない特性になってしまうという状況で、まだ、MOSFETを超えるデバイスはできていない。

神経系を模した左下のようなネットワークを右側の図のようにメモリスタのアレイでシナプスを作り、スピントランジスタでコンパレータを作り、それを使うADCでニューロンを作る。このようにすると、高密度で低電力のニューラルネットワークを作れる。

「Transynapse」は複数の入力の和をとって積分するデバイスであるが、それに加えて確率的な動作をする。そして、MTJを挟んだリード端子から出力を読み出す。

この素子が実現できると、確率的な推論を行うBelief Networkがコンパクトに作れるようになる。

これらのニューロネットワークは、デバイスモデルを使ったシミュレーションで、その動作やスイッチング速度、スイッチエネルギーなどが評価されているが、まだ、実証はされていない。

「Energy Efficient Computing: from Devices to Architectures」という活動では10州にまたがる15の大学で研究を推進している。

新しいデバイスと、それを使う新しいアーキテクチャの提案は相次いでいる。FET素子とそれを使う回路という"box"の外に出てみると、探索すべき場所の非常にたくさんあると述べてTheis教授は講演を締めくくった。

個人的感想であるが、CMOSのゲートを置き換えるようなスイッチを作るという努力は、まだ、解の糸口が見つからず苦戦をしている状況である。一方、スピントランジスタとメモリスタアレイで構成したニューラルネットのように、新しいデバイスを新しいアイデアで使うニューラルネットワークのように、ゲートよりももっと大きなサブシステム単位でエネルギー効率の高いものを実現するという方が成功の可能性が高いという印象である。

しかし、異なるアーキテクチャ、異なるデバイスを使うサブシステムを集めてコンピューティングシステムが作れるのかという懸念もあり、まだまだ、Beyond Exascaleの世界に至るには大きな障害があるように思われた。