既報の通り、ARM TechCon 2016でARMは新しく「Cortex-M23/33」と、これをサポートするAMBA 5 System IPであるSIE-200、さらにサブシステム全体を含んだSSE-200を発表した。これについてもう少し細かい話をご紹介したい。

Cortex-M23およびCortex-M33は、Mike Mullerの基調講演の中でアナウンスされた(Photo01)。実はTechnical Sessionを含めてこのCortex-M23/33の細かな話が一切明らかになっていないのだが、すでにARMの製品ページで概要は明らかにされている。基本的な命令セットなどは以前レポートしたとおりであるが、

- Cortex-M23:ARMv8-M BaselineをサポートするMCUコア(Photo02)。製品としてはCortex-M0+の後継にあたる

- Cortex-M33:ARMv8-M MainlineをサポートするMCUコア(Photo03)。製品としてはCortex-M3/Cortex-M4の後継にあたる

|

|

|

|

Photo02:目新しいのはWake-up Interrupt Controllerで、おそらくはサスペンド状態からの復帰を行うためのものが標準で追加されたというあたりではないかと思う |

Photo03:少なくともDSPおよびFPUはオプションであることがはっきりしており、両方を抜けばCortex-M3相当、両方を入れればCortex-M4(M4F)互換ということだろう |

の2製品で、Cortex-M7の後継は現時点ではまだリリースされていない。内部構成あるいはゲート数なども現状発表されてはいない。ただ性能に関しては公開されており(Photo04)、既存の製品より若干底上げがなされているという話になっている。

細かい話で言えば、まずCortex-M33のFPUは、基本的にはCortex-M4のものに近いが、互換という訳ではなく若干の改善がなされているが、Cortex-M7互換(=Double Precisionをサポート)では無いらしい。また、Photo02/03に示されているブロックのどこまでがImprementation Optionなのかも現在ははっきりしない。また後述するが、Cortex-M23/33はFast ModelとFPGAの両方がサポートされる。つまりFPGA上にCortex-M23/33を実装し、必要ならそれを最終製品として出荷することも可能であり、これに対応したライセンスも提供されるという話であった。

ということで話をSIE-200とSSE-200に移したい(Photo05)。これは言ってみれば昨年発表されたIoT Subsystem for Cortex-M Processorのセキュア版ということになる。SIE-200はSystem IPで、SSE-200はSIE-200を含むサブシステム全体という形だ(Photo06)。

|

|

|

|

Photo05:セキュアIoTプラットフォームという呼び方になっているが、これはIoTプラットフォームにTrustZoneの機能を付け加えたという形か |

Photo06:この図を見る限り、今後はPOP IPも提供されると思われるが、今回はそこまでの話はなかった |

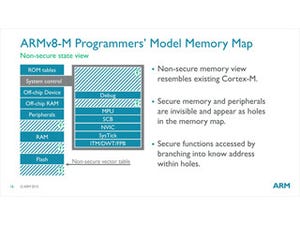

そのSIE-200の構成はこんな形になる(Photo07)。AHB5は基本的にすべてがセキュアの形でデータ転送が行われることになる。そのため、非セキュアなブロックを接続する場合は、Security Wrapperを提供することでセキュア化する形で実装される。このケースで、非セキュアなブロック(Photo07で言うところの緑のブロック)同士は問題なく通信が出来るが、セキュアなブロックへのアクセスは防御される形だ。またAHB5というよりはTrustZoneの機能かもしれないが、アクセスの際にはメモリアドレスをベースに保護が行われることになる(Photo08)。

このSIE-200を中心に、必要となるサブシステムIPをさらに集約したのがSSE-200である(Photo09)。先ほどのPhoto06にも出てきたが、MCUコアとSIE-200に加えてCryptoCoreやCordio IPなどをまとめたのがSSE-200となる。具体的にはハードウェアIPとしてはCPUコアとSIE-200、Cache & Memory、Debug & Power infrastructure、CryptoCell、Cordioが用意され、これに対応するソフトウェアとしてmbed OSとセキュアライブラリ、ドライバー、プロトコルスタックなどが挙げられる。これを利用した例がこちら(Photo10)で、Dual Cortex-M33コアのSoCが比較的簡単に構築できるとしている。

このSSE-200であるが、ターゲットプロセスはTSMCとUMCの40nm ULPということであり、また開発リスクを最小にするためにSSE-200全体をFPGA上に実装できる(Cordioは除く)(Photo11)。実際会場では、Photo10の構成(ただしシングルコア)をFPGA上で動作させて、TrustZoneのデモが行われていた(Photo12)。このプロセス回りの話は別途レポートしたい。

|

|

|

|

Photo11:これらのメリットは以前のIoTサブシステムと同じだが、FPGAで全部を動かすことは出来なかった |

Photo12:現在は非セキュアな状態で、デバッガ経由でメモリの中身がアクセスできる。これが右のスイッチをセキュア側にすると、TrustZoneによってデバッガからのメモリアクセスが防御できるという簡単なデモである。実際セキュア状態ではデバッガからメモリアクセスが出来なくなっていた |

ちなみにこのCortex-M23/33の発表にあわせてルネサス エレクトロニクスは次世代Renesas Synergyプラットフォームを発表したが、会場でそのデモが行われていた(Photo13)。とはいえ、今回はFPGAの上でCortex-M23といくつかの周辺回路を動かしただけの状態。説明員に根掘り葉掘り聞いてみたところ、「これはフルファンクションの次世代Synergy?」という問いには「No、MCUコアとメモリと、あとはいくつかの周辺回路を搭載しただけ」と言う回答であった。また、「いつシリコンが出るの?」という問いには、「申し訳ないがそれは今は何もいえない」となり、「それぞれ既存のSynergyのどのラインアップ(Synergy S1/S3/S5/S7)の後継になるの?」という問いにも「申し訳ないがそれは今は何も(略)」、「もうそれぞれの製品の最終仕様は決まったの?」という質問も、「申し訳ないがそれは今は(略)」、「Synergyはプロプライエタリのセキュリティ機能を持っているけど、これはARMv8-MのTrustZoneとどうマイグレーションされるの?」という質問についても、「申し訳ないがそれは(略)」、「逆にSynergyのプロプライエタリのセキュリティ機能を使わずにTrustZoneを直接利用することは可能なの?」、「申し訳ないが(略)」、「次のRenesas DevConまでにはこの辺の詳細は明確になるの?」、「申し訳(略)」、ということで、現状はとりあえずFPGA上でCortex-M23を動かしてみた、という以上のデモではないようだ。ちなみにFPGAでこれをCortex-M23/33を動作させた例は会場でも他にいくつかあった(当然ながらARM自身もCortex-M33のFPGA上での動作デモを行っていた)。