NVIDIAはHot Chips 28において、次世代のTegraプロセサである「Parker」の発表を行った。Parkerは開発コードネームで、正式発表の際には「Tegra TP1」というような名前になると思われるが、現状では、まだ、発表されていないので、ここではParkerを使うことにする。

次の図のように、Parkerは2個の「Denver 2.0」コアと4個の「Cortex-A57」コアとPascalアーキテクチャの256 CUDAコアのGPUと各種の固定機能を集積したSoCである。そして、TSMCの16nm FinFETプロセスで作られている。

|

|

|

Parkerは2個のDenver 2コアと4個のCortex-A57コア、そして256CUDAコアのPascal GPUを搭載し、さらに各種の固定機能ブロックを集積したSoCである (このレポートの図は、すべてHot Chips 28でのNVIDIAの発表スライドのコピーである) |

NVIDIAはKepler GPUベースのTegra TK1、Maxwell GPUベースのTegra TX1を作り、そして今回のPascal GPUベースのParkerは3代目に当たる。TX1もParkerも256 CUDAコアであるが、TX1では1TFlopsであった演算性能を1.5TFlops(FP16)に引き上げている。そして、自社開発のDenver 2コアはDenver 1コアに比べて30%性能/電力が向上しており、スーパーコアとビッグコアの組み合わせとなっている。

ここでGPUの演算性能をFP16で記述しているのは、ディープラーニング用のFP16の性能を重視している表れである。

また、自動車用途では重要なカメラ台数をTX1の6台から倍増して12台としている。メモリも128bit幅のLPDDR4をサポートし、約50GB/sのメモリバンド幅を実現している。そして、メモリにECCを付けているところが、エラーに対する許容度の小さい用途を想定していることをうかがわせる。

そして、Parkerではインタフェースとして自動車用の制御ネットワークであるCANが2本サポートされ、自動車レベルのエラー耐性やセキュリティーがサポートされて自動車に使えるSoCになっている。また、仮想化も各サブシステムを独立して動かすために重要な機能である。

初代Tegraは何に使うのか的がはっきりせずNVIDIA製のゲーム機などを作り、2代目は組み込みを主力に据えた。3代目のParkerは、組込用途向けということは2代目と同じであるが、自動車搭載に的を絞った感がある。まだ、自動運転車のビジネスは立ち上がっていないが、4代目か5代目のTegraを作るころには立ち上がりそうな有望分野である。

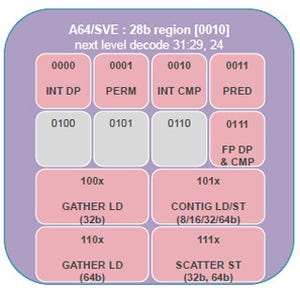

ParkerのCPU部分は、2個のDenver 2コアと4個のARM製のCortex-A57コアで構成されている。そして、独自設計のコヒーレンシ維持機構で、2コアのDenver 2と4コアのcortex-A57をコヒーレントに接続している。

Denver 2はARMコアの中では最高の性能を持ち、Denver 1と比較して電力あたりの性能は30%向上しているという。

次の図はSpecInt2000_rate性能の比較で、Denver 2の2コアを1として、Appleの2コアA9X、Huaweiの4コアA72は65%程度の性能、Qualcommの4コアKryoは40%弱、Samsungの4コアM1は60%弱の性能と言う。この比較を信じれば、Denver 2は、NVIDIAが言うようにARMコアでは最強である。また、2コアでこの性能であるので、シングルスレッド性能では、さらに優位と思われる。

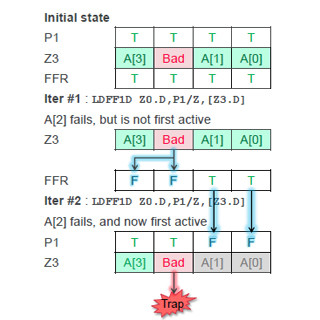

Parkerではハードウェアで、仮想化をサポートしており、2段階のアドレス変換を行うMMUを持ち、不法なメモリアクセスをチェックしている。そして、GPUのMMUも多数のチャネルのコンテクストを厳密に分離している。

また、GPUがPascalになって、命令境界でプリエンプションができるようになり、仮想化が使い物になるようになったことも大きい。

Parkerでは、自動車の電気/電子システムの機能安全の国際規格であるISO 26262準拠となった。そして、エラー検出やエラー訂正の機能を充実している。さらに、セーフティエンジンという機能を備え、2個のParkerチップを使って、ロックステップで動作させ、エラー検出を行う機能も装備している。

また、DRAMのエラーもセーフティエンジンに通知され、スクラビングや故障部分の切り離しを行う。当然、Denver 2チップ内部のキャッシュなどのメモリにはECCやパリティの保護が付いている。

そして、デュアルCANインタフェースやEthernet AVBのネットワークを備える。というように、Parkerは自動車用のSoCになっている。

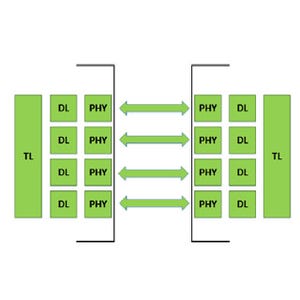

|

|

|

Parkerは自動車の電気/電子システムの機能安全の国際規格であるISO 26262規格に準拠し、各種のエラー検出、訂正機能を備えている。また、CANやEthernet AVBなどの自動車用のネットワークをサポートしている |

Parkerを使う「Drive PX 2」は、Parkerを2チップ搭載し、ロックステップで高信頼のシステムを作ることが出来る。それほどの高信頼が必要でない場合には、2チップで合計12コア、2GPUで最大8TFlopsの浮動小数点演算性能が得られる。また、ディープラーニングの演算は24DL Topsの性能までスケールできる。

また、ISO 26262のSEooCの考え方にそって、セーフティマニュアルを提供し、顧客がシステム全体の安全性を実現することを助ける。このため、Drive PX 2は多くのOEMやTier 1パートナに採用されている。

|

|

|

Drive PX 2はParker 2チップ、ディスクリートGPUを2チップまで拡張可能。安全性の実現に関しても、SEooCの考えに準拠している。結果として、多くのOEMやパートナに採用されている。なお、Drive PX 2は水冷で、右端の丸いコネクタは冷却水の入りと出である |

Parkerを使うDrive PX 2のブロックダイヤを次の図に示す。Drive PX 2はParker、GPUなどが2重になっており、同じ動作をさせて出力を比較するロックステップ動作をさせて、高度なエラーの検出を行うことも出来るようになっている。

まとめとして、Tegra ParkerはDenver 2 CPUコアの採用により、性能/Wを改善している。そして、big(A57)とsuper(Denver 2)CPUコアの組み合わせで非常に高い性能を実現している。Heterogeneous Multi Processorアーキテクチャで、プログラミングが容易、最新のPascalアーキテクチャのGPUを内蔵している。

その結果、自動車用SoCとして、高い柔軟性を備えている。と、まとめを述べた。