Hot Chips 28 - NVIDIAのPascal GPUの実装とNVLink(前編)はコチラ

独自の高速のNVLink

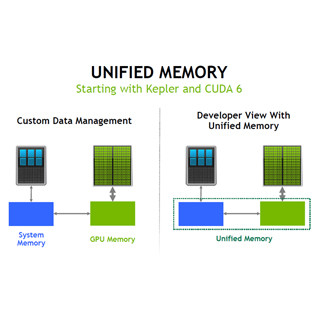

NVIDIAは、PascalからNVLinkと呼ぶ独自の高速リンクを装備するようになった。NVLinkは物理的には、ペアの信号線を使う差動信号で20Gbit/sの伝送を行う。この伝送速度は、PCI Express 3.0の2.5倍である。1本のNVLinkチャネルには、このペアを8ペア使う20GB/sの伝送路が両方向に存在する。つまり、全体では16ペアの信号線で、20GB/s+20GB/sの伝送を行う通信路である。

信号線は、直流結合で、85Ωで終端されており、ビット誤り率は10-12であるという。しかし、40GB/sは320Gbit/sであり、このビット誤り率では3秒に1回エラーが発生する。そのため、CRC(Cyclic Redundancy Check)でエラーを検出し、エラーが発生したパケットを再送してエラー回復を行っている。

NVLinkは、1回の伝送では最大256バイトのデータを送ることができ、256バイト伝送の場合、データ伝送の効率は94%であるという。

この、NVLinkを使用してGP100同士、あるいはNVLinkをサポートしているIBMのPOWER8チップとの接続を行うことができる。

NVLinkのFlitは128bitで、パケットは、ヘダーなどを含むFlitと、最大16Flitのペイロードで構成される。そして、必要に応じて、Address Extension FlitとByte Enable Flitを含むことができる。しかし、これらの追加のFlitについての詳しい説明は無く、詳細は不明である。

|

|

|

NVLinkは128bit長のFlitを使っている。そして、1つのパケットは、1Flitのヘダーなどと最大16Flitのペイロードを送る。オプションで、Address Extension FlitとByte Enable Flitを含むことができる |

次の図は単純な64バイトの読み込みのトランザクションを示したものであり、要求元から64バイトREAD REQパケットを送り、ターゲットは、4Flitのデータに64バイトREAD RESPヘダーを付けて要求元に送り返す。

各パケットには25bitのCRCが付けられており、最大5bitのランダムなエラー、あるいは、1レーンの中で最大25bitの長さのエラーを検出することができるようになっている。エラーが無い場合は、受信側は送信元にアクナレッジを返すので、アクナレッジが無ければエラーが発生したとみなして、送信元はパケットを再送する。

なお、この図に見られるように、CRCは現在のヘダーと前回のペイロードに対して計算されている。

NVLinkの伝送効率は、256バイトのパケットの場合は、約90%となっている。

次の図はNVLinkを使って8台のP100 GPUを接続する例で、4台のP100を完全結合で接続し、これを積み重ねて対応する位置にある上下のP100を、残る1本のNVLinkでつなぐという構成になっている。この構成では同一面内の4つのP100は1ホップで到達でき、上下をまたぐ場合は、もう1ホップが必要となる。それでも、8台のGPUの中では、最大でも2ホップで通信ができるという構成となっている。

この構成では、CPUはNVLinkのインタフェースを持っておらず、PCIスイッチ経由でPCI Expressで接続されている。この構成は、NVIDIAがディープラーニング向けの開発システムとして販売しているDGX-1で実際に使われている。

CPUとして、IBMのPOWER8やPOWER9を使えば、これらのCPUはNVLinkをサポートしているので、P100とCPUをNVLinkで直結することができる。しかし、NVLinkはGPUを制御する機能は持っていないので、CPUとGPUを接続するPCI Express接続は必要である。

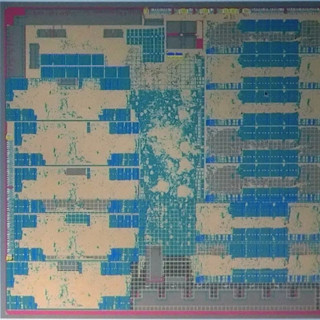

今回の発表では、本物のチップ写真が公表されたことは嬉しいことであった。また、P100 GPUの実装など物理的な話が多く、興味深い発表であった。