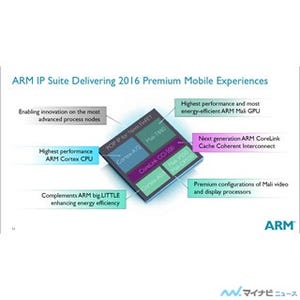

英ARMは、同社の次世代コアである「Artemis」を利用したテストビークルについて、TSMCの10nm FinFET(10FF)プロセス向けにテープアウトした事を発表した。これに関する細かい説明があったので、お届けしたい(Photo01)。

そもそもARMは複数のファウンドリと協業、あるいは戦略的提携を多く結んでいるのはご存知の通り。特に先端プロセスに関しては非常に熱心である。10nm世代に関しては2014年10月に複数年の協業が発表されており、2016年3月には7nm FinFETに関する協業も発表されている。今回の発表は10nmに関する話で、こちらでは早ければ2015年第4四半期に顧客がテープアウトできることを目指すとしていた。実際にはもう少し時間がかかっているが、2016年のDACでARM/TSMC/SynopsysがCorte-A72の16/10nm Reference Imprementationの公演を行う事が予告されているから、やや遅れているとは言え順調ではある。

これとは別に、ARMは常に最新プロセッサを最新のプロセスでインプリメンテーションを行う(Moore氏)事を心がけており、今回はこの話が紹介された。

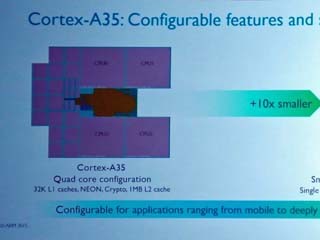

さてArtemisというコアは、2015年11月に開催された「ARM TechCon 2015」でコード名だけが発表されている。実際今回もコアそのものに関する話はほとんど無しであるが、ロードマップで判る通りCortex-A72の後継製品という位置づけにある。要するにbig.LITTLEのbig側のコアという位置づけだ。ただ今回は製品向けインプリメンテーションではなく、あくまでもPPA(Power/Performance/Area)のベンチマーク用ということで、構成はPhoto02の様になっている。

|

|

|

Photo02:Quad core ARM Cortex-AがArtemisコアである。Mali GPUの方は詳細は不明であるが、おそらくMidgardアーキテクチャのどれかではないかと思われる。Cortex-M0側はデータを取るためのものであろう |

さて、ここからが発表の本題である。今回テープアウト10nm FinFETでのテストベッドの結果を、16nmの場合と比較したグラフがこちらである(Photo03)。横軸がパフォーマンスでこれは動作周波数、縦軸が消費電力でこれはスタティック電力(リーク)+ダイナミック電力の合計である。比較した場合、消費電力が同じなら11~12%ほど動作周波数を引き上げることが可能で、逆に動作周波数が同じなら最大30%ほど消費電力が低減できることが示されている。

ちなみにPhoto02は同じArtemisコア同士でプロセスを変えた場合にどうか、という話である。では既存のCortex-A72との比較はどうか? という結果も別途示された。まず動作周波数で言えば

| 電圧 | Cortex-A72 16FF+ |

Artemis 10FF |

|---|---|---|

| Vnom-10% | 1.94GHz | 1.82GHz |

| Vnom | 2.6GHz | 2.34GHz |

| Vod | 2.78GHz | 2.49GHz |

| Vsod | 3GHz | 2.7GHz |

ということで、10FFのAltemisの方が平均1割程度、動作周波数が低い形になっている。もっともこれはArtemisの10FFのPDKがVersion 0.5という早期のものであることも無関係ではないだろうが、とりあえず現状では動作周波数はやや低いところに留まっている。ただしVnomにおける性能/消費電力比で言えば、Artemisの動作周波数あたりの消費電力(主にダイナミック電力)はCortex-A72の半分程度に収まっている。リーク電力はCortex-A72が50mW程度、Artemisが40mW程度であるが、ダイナミック電力はCortex-A72が270mW/GHz程度なのに対し、Artemisは130mW/GHzほどに納まっている。これを元にざっくりざっくり試算すると、Cortex-A72はダイナミック電力が2.6GHz動作で680mW+スタティック電力が50mWほどで、730mW前後といったあたり。

一方Artemisは2.34GHz動作でダイナミック電力が330mW+スタティック電力が40mWといったところで、合計で370mW程度。定格動作で比較すると消費電力がほぼ半減していることが判る。これだけマージンがあれば、同じ消費電力枠ならまだArtemisの方は相当動作周波数を引き上げる余地があることになる。

ちなみにこの10nmや次の7nmでもARMはPOP(Processor Optimization Package)を提供する予定であるが、ちょっとここで戦略の変更が行われたようだ。従来POPはあるプロセス/プロセッサの組み合わせで基本的に1種類しか存在しなかったが、今後はハイパフォーマンス向けと低消費電力向けの2種類のPOPが提供されることになるらしい。

また、冒頭の2014年10月の発表にもあったが、ARMとTSMCの協業は単にCPUのコアのみならずArtisan Physical IPの提供も含むとされており、こちらの準備も順調に進んでいるという話であった。