ベルギーの半導体・ナノテクノロジー研究機関imecと 米国の半導体プロセス開発ツール・サプライヤ「Coventor」は12月7日(米国時間)、半導体デバイスの国際会議「International Electron Device Meeting(IEDM)」の開催に合わせて、両社の共同開発チームが、7nmロジック集積回路だけではなく、3次元NAND型フラッシュメモリ、 STT-MRAM(スピン注入磁化反転:spin transfer torqueの原理を用いてデータ書き換えを行う磁気抵抗変化型ランダム・アクセス・メモリ)など、すべての7nmデバイス開発に、Coventerの半導体プロセスモデリング・プラットフォーム「SEMulator3D」を利用し、開発期間の短縮ならびに試作コスト削減を目指した取り組みを進めると発表した。

SEMulator3Dは、フォトマスク作製用の回路パターン・レイアウト図面とプロセス記述表から、自動的に3次元のデバイス構造図を出力する一連のプロセス・モデリング・ソフトウェアで構成されたプロセスモデリング・プラットフォームである(図1)。

imecの次世代プロセス技術開発担当シニアVPのAn Steegen氏は「SEMularoe3Dの力を借りて、7nmの半導体集積化とプロセスの問題を解決することが可能となった。今回の協業により、半導体メーカーが新たなプロセスを導入する際のリスクを軽減し、歩留まり向上や試作コストを削減することに貢献するだろう」と述べている。

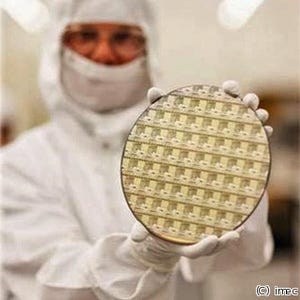

imecがベルギー・フランダース地方政府の資金で、同キャンパス内に建設中の450mmクリーンルーム(関連記事参照)が2016年2月に竣工と同時に(450mmウェハ使用はまだ時期尚早なため)7~5nmデバイス用300mmプロセス装置を搬入し、各種7nmデバイスの試作と、すでにテープアウト(設計完了)している5nmテストチップの試作を行う。それまでは、SEMulator3Dを用いてコンピュータ上で仮想的な試作を行うようだ。実際に多数の300mmウェハを用いてプロセスの最適条件を見出す手間が省けるので、開発期間短縮がはかれ、開発コストを削減でき、より早く成果を出せると言う。

imecがIEDMで記録的な23件の論文を発表

imecは、今週、米国の首都Washington D.C.で開催中のIDEM(米国電気電子学会IEEE主催)で、5nmおよびそれ以降のデバイスの基礎となる新プロセス・デバイス技術に関して記録的な23件の論文を発表した。この中には以下の3件のような画期的な発表が含まれている。

- n型シリコン基板上に1.5Ωcm2という低コンタクト抵抗を実現。Pの活性化を増進するダイナミック表面アニール(DSA:dynamic Surface Annel)、Geの事前非晶質化、Tiシリサイド化などの新手法導入により可能になったという。

- Pド―プ・シリケートガラス(PSG)の拡張ドーピングを用いてNMOSシリコンバルクFinFETのアクセス抵抗低減を実現。これにより、Fin構造のサイドウォールへのドーピングをダメージなしで均一に行えるようになった。

- 接合の無いhigh-k/metal gate(HKMG)オールアラウンド・InGaAsナノワイヤFETを300mmシリコンウェハ上で実現した。ナノワイヤをゲート電極で完全に取り囲んだGate-All-Around(GAA)構造を採用するとゲート電界による電流制御性が改善し、高ON/OFF比のFETが実現できるため、次世代トランジスタ構造として期待が高まっている。

imecのLuv Van den hove社長は、「IEDMで23件もの論文発表が行えることは、imecが先端半導体研究開発で世界をリードしている証であり、誇りに思う。23件のうち、10件はシリコンCMOS技術を7nm以降まで延長させる正統的な技術とは異なるアプローチの新たな取り組みである。私たちはシリコンCMOSを超えた(beyond CMOS)技術開発にも取り組んでおり、スピントロニクスや2次元機能性ナノ材料にもすでに手掛けている」と述べている。