既報の通り、ベルギーimecとEDAベンダであるCadence Design Systemsは5nmプロセスを用いたテストチップの設計を完了した(テープアウト)。2015年10月時点で最先端プロセスとなる5nmのテープアウトはいかにして実現されたのか、imecで5nmテストチップの設計を担当しているプリンシプル・エンジニアのPraveen Raghavan氏(写真)にインタビューする機会を得たので、詳細をお届けしたい。

――具体的的にEUVリソグラフィとArFリソグラフィはどのように使い分けるつもりか?

次のような3通りの方法を試そうと思っている。

- SAQP(自己整合4重露光) 193i(波長193nmのArF液浸リソグラフィ)でライン・パターンを形成し、カットマスク・パターンやビアはEUVリソグラフィを用いてて1回露光でパターニングする。

- SAQP 193iでライン・パターンを形成し、カットマスク・パターンやヴィア形成には193iの多重露光を用いる。

- ラインもビアもすべてEUVリソグラフィだけでパターニングする。SAQPを用いないので、カットマスクは必要ない。

――テストチップは具体的に何か?

マイクロプロセッサとそのためのTEGだ。

――用いたEDAツールは?

Cadenceの「Innovus Implementation System」という最新型の配置配線ツールを用いて、5nmに向けてデザインルール、ライブラリ、配置配線技術をCadenceと一緒に最適化した。

SoC開発者がInnovus Implementation Systemを用いて設計すると最適なPPA(Power/Performance/Area:消費電力・性能・および専有面積)が得られると同時にTTM(Time To Market)を加速できる。大規模並列処理アーキテクチャにより、従来のツールに比べてPPAが1~2割改善され、フロー全体で実行速度を高速化しながら大きな回路規模への対応を実現できるフィジカル・インプリメンテ―ション、システムだ。

――ニュースリリースに添付されている図面は何か?

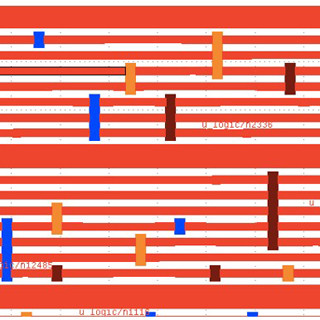

9トラック・ライブラリを使ったM2(最下段から数えて2番目のCuメタル層)の配置配線例だ。M2は下から2番目のメタル層だが、最初のルーチンなメタル層である。M1はタングステンのコンタクト層が含まれていて複雑で、ルーチンなパターンではない。図の中で、規則的に並んだ赤い横線がM2のラインで、色付けされたさまざまな縦のバ―はカットマスク・パターンである。 これによってM2ラインをカットして所望の回路パターンを得るわけだ。

最初に述べたリソグラフィ手法の(1)では、カットマスクパターンはEUVを用いて1回露光で形成できる。(2)ではカットパターンは193iを用いて多重露光で形成する。(3)ライン形成にもビア形成にもEUV用いる場合は、直接M2パターンを形成できるのでカットマスクパターンは無用である。