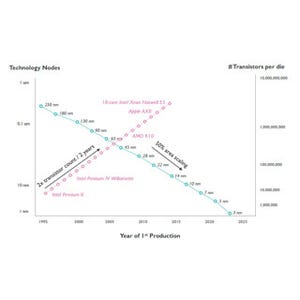

ベルギーの独立系半導体・ナノテク研究機関であるimecと米国のEDAベンダCadence Design Systemsは10月7日(現地時間)、世界半導体業界ではじめて、5nmテストチップのテープアウトを完了したと発表した。EUV(波長13.5nm)リソグラフィと自己整合4重パターニング(Self-Aligned Quadruple Patterning:SAQP) ArF(波長193nm)液浸リソグラフィを併用することを前提にパターン設計されている。

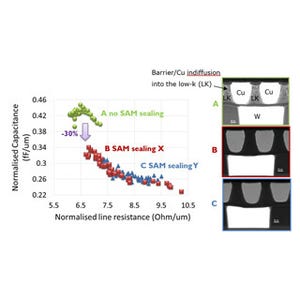

imecは、Cadenceの最新型配置配線ツール「Innovus Implementation System」を用いて消費電力・性能・および専有面積(Power/Performance/Area:PPA)を最適化している。メタル・ピッチは従来の32nmから24nmへ縮小し、パターニングの限界を押し下げている。

imecのプロセス開発担当シニア・バイス・プレジデント、Ann Steegen氏は「Cadenceとの協業により、テープアウトに必要な技術を共同開発し、5nmおよびそれ以下の寸法の世界で最も微細化されたパターンを含むテストチップを開発できた。Cadenceの次世代EDAプラットフォームの寄与が大きい」と述べた。一方、Cadenceのシニアバイス・プレジデントAnirudh Devgan氏は、「imecのプロセス、デバイス技術とCadenceの設計ツールにより、超微細構造の次世代モバイルおよびコンピュータチップを開発するための手順を確立することができた」と述べている。

著者注:米Intelは10nmプロセス・デバイスを開発中であるが、そんな中、2015年7月16日、IBMが世界で初めて動作可能な7nmテストチップ試作に成功したと発表し、業界関係者を驚かせた。微細化に関してIBMの宿敵であるベルギーimecは、今回5nmテストチップのテープアウト完了を発表。テスト・デバイス試作はこれからだが、対抗上、動作確認まで待てなかったのだろう。ちなみに、imecで微細化を陣頭指揮するAnn Steegen SVPは、2010年12月、imecがIBMのニューヨークの半導体研究開発部門から引き抜いた女性研究者である。微細化は決して未だ終焉しておらず、世界最先端研究機関による熾烈な微細化競争はまだまだ続く。