富士通研究所は、サーバに搭載したCPU上で、ソフトウェアの各処理で消費される電力を詳細に算出し、省電力プログラミングを実現する技術を開発したと発表した。

低消費電力化にはハードウェアによる低電力化に加え、サーバ上で動作するプログラムの消費電力を低減する方法があり、消費電力を抑えるプログラミングを実現する前提として、ソフトウェアが消費する電力を把握する必要がある。

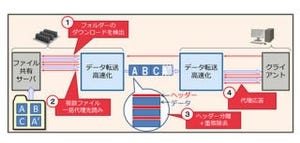

Intel製CPU搭載サーバでは、電力制御のためのRAPLという機構を使って、CPU全体の消費電力は計測できるが、富士通では、CPUコアごとに採取可能なクロック数やキャッシュヒット率などの情報を活用して、プログラムのモジュール単位など詳細に消費電力を推定する技術を開発した。

具体的には、CPUコアごとに採取可能なクロック数やキャッシュヒット率といった計測値を組み合わせ、消費電力と相関の高い性能指標を新たに考案。算出したCPUコアごとの値にしたがって、CPUの消費電力を各コアに配分することで、プログラムのモジュール単位などの詳細な消費電力が把握できるという。

性能指標に使用するCPUコアごとの計測値を数種類に絞ることで、1ミリ秒という細かさで採取でき、また、電力情報算出時のオーバーヘッドを全体の1%程度に抑えられるため、計測が性能値に与える影響もほとんどないという。

今回開発した技術は、ソフトウェア開発者が消費電力を削減するチューニング(省電力プログラミング)に活用できる。富士通研究所は、本技術の2016年度の実用化を目指し、ソフトウェアによる消費電力削減の実証を進め、富士通のデータセンターへの技術適用も検討し、消費電力をさらに詳細に分析することで、データセンターの省電力化を目指す。