ベルギーの半導体・エレクトロニクス研究機関imecは、7月14~16日に米国カリフォルニア州サンフランシススコで開催された半導体装置材料展示会「SEMICON WEST」において、次々世代プロセスとなる5nmおよびそれ以降の半導体ロジックデバイス製作に向けた多層配線の超多孔質low-k膜の新しいシール手法の基礎検討結果を発表した。

超多孔質low-k膜は、雰囲気中の水分(=超高比誘電率物質)やメタル配線材料の銅やALD/CVDメタルバリア・プリカ―サ―が、その後のウェハプロセス中に、多孔を通して膜内に浸透拡散し、low-k膜のk値を高めるとともに、リーク電流を高め、絶縁耐圧を下げてしまう問題があり、この対策が求められている。

imecの手法は、有機単分子膜を自己組織化させて多孔質low-k膜の孔をシールし、水分やメタルプリカ―サーの浸透・拡散を防ぐだけではなく、銅を銅配線のなかに押しこめ、相関絶縁膜中への拡散を防止する。

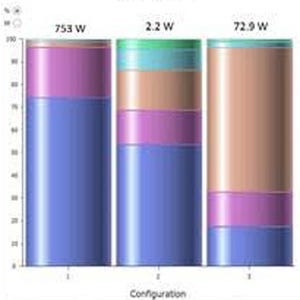

自己組織化単分子膜(Self-assembled monolayers:SAMs) はシラン由来の物質で、CVD(化学的気相堆積)あるいはALD(原子層堆積)法により300mmウェハに気相で堆積する。その後、銅配線プロセスを行う。シール層のk値(比誘電率)は3.5、厚さは1.5nm以下。これにより5nmプロセスノード以降のRC遅延を抑えることができる。SAMシールによりキャパシタンスは約3割減少できる。絶縁耐圧の向上も確認されている。

これらの実験は、ハーフピッチ45nmの配線パターンを用いたフィ―ジビリティスタディ(実現可能性確認実験)であり、今後、研究パートナーのGLOBALFOUNDRIES、Intel、Micron Technology、パナソニック、Samsung Electronics、SK Hynix、ソニー、TSMCとともに、5nm世代以降の実用化めざして技術の完成度を高めるという。