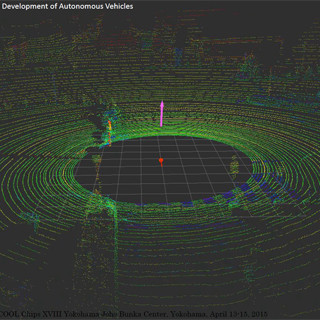

COOL Chips XVIIIにおいて、ARMのテクノロジとシステムのディレクタのJohn Goodacre氏が「Riding the Perfect Storm, Bringing Mobile Compute to the Data Centre」と題して基調講演を行った。Goodacre氏は、マンチェスター大学の教授でもある。

|

|

|

EUROSERVERについて基調講演を行うJohn Goodacre教授 |

「Perfect Storm」は、発達した温帯低気圧にハリケーンが合体するという悪条件が重なってできた最悪の嵐に漁船が立ち向かうという2000年に米国で作られた映画の題名から取られている。微細化のムーアの法則も行き詰まりを見せ、消費電力も減らないなどPerfect Stormの状況をどう乗り切るかという講演である。なお、余談であるが、Perfect Stormのモデルとなった漁船は、困難な状況を乗り切れず沈没したと見られている。

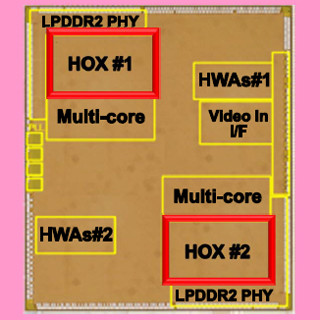

ヨーロッパは、「EUROSERVER」というプロジェクトを推進している。このプロジェクトはARMが中心となり、研究機関、大学、企業などがメンバーとなって推進されており、組み込みからHPCまでの広範囲な市場に適したスケーラブルでコスト効率の良い、ARMベースのマイクロサーバの開発を目指している。

COOL Chips XVIIIの記事一覧はコチラ |

|---|

次の図の左側は大型の300mm2のチップ、右側は50mm2の小さなチップを2.5D実装する場合の集積回路のコストを示している。300mm2のチップはウェハ1枚に80個しか作れず、歩留まりは10%程度になるので、1個800ドルにつく。これに組み立て時の歩留まりを考えると、最終的には840ドルとなる。一方、50mm2のチップは、ウェハに1300個載り、同じ欠陥密度を想定すると、歩留まりは85%になるので、1個8ドルでできる。このチップを4個搭載するインタポーザは、チップ1個あたり6ドル程度で作れる。これに2.5D実装のコストや歩留まりを含めても50ドル程度であり、同じ計算能力とIO能力を単一の大きなチップを作る場合は1/10~1/20のコストで実現できるという。

ただし、左は300mm2のチップであるのに対して、右は4個のチップで合計200mm2とチップ面積が小さい。また、 ウェハ1枚に300mm2のチップが80個なら1/6の面積のチップは80×6=540で、ウェハは円形であるので小さいチップの方が周辺部が切れてしまうという損失が減るという効果はあるが、1300個は搭載できない。

さらに、8ドルのチップと6ドル/dieのインタポーザであるので、4チップ分では56ドルとなり、これに組み立てコストが加わるので、~50ドルは安めの見積もりである。ということで、不公平な比較ではないかと思うが、ここでは、発表の通りに紹介する。

次の図はシステムの各コンポーネントが1bitの情報を処理するのに要するエネルギーを示すもので、上側の青線は現在、下側の赤線は2018年の消費エネルギーを示している。そして、左から倍精度の浮動小数点演算(これだけは64bit)、レジスタ、チップ上の1mmの配線、チップ上の5mmの配線、チップ外のDRAMのアクセス、近距離の接続、システムを横断する接続で1bitの情報を扱うのに必要なエネルギーを表している。このように、2018年レベルでは、倍精度浮動小数点演算に必要なエネルギーは5mmのチップ内配線を通して信号を送るよりも少なくなっている。

なお、右の図ではDRAMアクセスは1000~2000pJ/bitであり、1GB(9bit×109≈1010bit)の読み出しでは1~2×1013pJとなり10~20Jとなるがスライドでは50~100mJとなっている。また、プリント板上の配線はグラフでは1~3mJ/bitであるが、Exampleでは100pJ、また、5mm配線はグラフでは30pJであるが、Exampleのところでは1pJとなっている。

EUROSERVERのシステムアーキテクチャは、1個あるいは複数の64bitアーキのARMプロセサをコヒーレントなL0リンクで接続したクラスタにHMC(Hybrid Memory Cube)をつけ、このグループを2個、L1リンクで接続したものが計算ノードとなる。また、L1リンクにはノードSSDとLocal IOが接続されている。そして、大規模な複数ノード構成の場合は、グローバルなL3リンクでノード間を接続する。

キャッシュコヒーレンシが保たれるのはL0リンクで接続されている範囲で、それより外側はL1以降のリンクで通信するGlobal Address Spaceのシステムである。

|

|

|

複数個の64bitアーキのARMコアをコヒーレントなL0リンクで結び、それにHMCメモリを付ける。これを2組L1リンクで接続する。この計算ノードにはNode SSDとLocal IOが含まれている。マルチノードにする場合はL3リンクで接続する |

(後編は5月20日に掲載します)

COOL Chips XVIIIの記事一覧はコチラ |

|---|