GTC 2015の関連記事 |

|---|

|

・【レポート】GTC 2015 - Deep Learningを理解する(前編) ・【レポート】GTC 2015 - Deep Learningを理解する(中編) ・【レポート】GTC 2015 - Deep Learningを理解する(後編) ・【レポート】GTC 2015 - 米国の次世代スパコン「Summit」 ・GTC 2015の記事一覧はコチラ |

筑波大学と東京大学(東大)のTCAに関しては2014年のGTCでも発表されているが、昨年は動き始めた時点での発表であり、実測データはあまり含まれていない発表であった。しかし、今年は1年を経過して、実測データを豊富に含んだ発表となったので、復習を兼ねた「システム構成編」実測性能をまとめた「システム性能編」をお届けする。

|

|

|

TCAについて発表する東大の塙准教授 |

GTCでは発表者は、昨年と同じ東大の塙敏博 准教授である。なお、HA-PACS TCAはもともとは筑波大のプロジェクトであったのであるが、主要メンバーの塙先生が東大に移られたので、現在では、両方の大学のロゴがスライドに載っている。

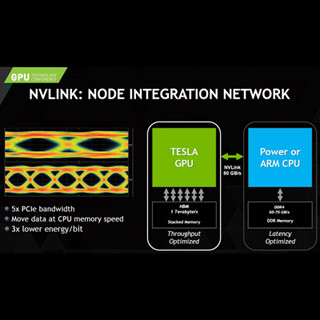

複数のGPUを使って処理を分担させようとすると、処理を分割した継ぎ目のところなどでGPU間でデータをやり取りする必要が出てくる。この場合、普通は、送り元のGPUのデータをDMAを使ってPCI Express経由でCPUのメモリに読み込み、それをDMAを使って、また、PCI Express経由で受け手のGPUに転送するという手順が必要になる。しかし、本来はCPUのメモリにデータを格納する必要はなく、GPUからGPUに直接データを送ることが出来れば効率が上がるはずである。

このような考え方で開発されたのが、筑波大の「PEACH」で、その2代目が「PEACH2」である。次の図のように、PEACH2はデータの伝送路としてはPCI Express 2.0を使い、PEACH2同士で直接通信を行うことができる。

PCI Expressは、通常はCPUに入っているマスタノードがその他のI/Oノードを制御して、マスタノードとの間でデータ転送を行うという動作をするのであるが、通信路としてはアドレスさえ指定すればどのノードとの間でも通信ができる構造になっている。PEACH2では制御の部分を独自に設計することで、CPUの介在無しに2つのGPU間で通信が行えるようになっている。

PACH2は4つのPCI Express 2.0 x8のポートを持っており、1ポートはCPUと接続し、残りの3ポートを他のPEACH2に接続する。Gen2 x8のPCI Expressは40Gbpsのバンド幅を持っており、QDR InfiniBand x4と同じバンド幅である。一方、プロトコルが簡単であるので遅延時間は小さい。

PEACH2はAlteraのFPGA「Stratix IV」で作られており、次の写真のようなPEACH2ボードと呼ぶPCIカードに纏められている。

そしてこのボードがサーバのマザーボードの上にメザニンカードとして搭載されている。

「HA-PACS(Highly Accelerated Parallel Advanced system for Computational Sciences)」は筑波大の計算科学研究センターの主要スパコンであり、学内外の研究者で共同使用されている。これに対してHA-PACS/TCAはJSTのAC-CRESTプロジェクトで作られたアクセラレータ間を直結するシステムを研究し、それを使うソフトウェアや並列言語やそのコンパイラを開発するためのシステムである。

HA-PACSのBase ClusterとTCAの諸元を次の表に示す。

TCAとBase Clusterは隣接して設置され、両者を一体化して動かすこともできるようになっている。

TCAのノードの構成は次の図のようになっている。

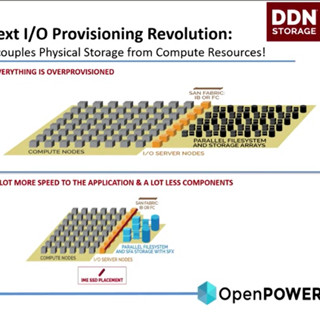

TCAの計算ノード間の接続は、次の図のようになっており、16ノードのグループを構成している。16ノードのサブクラスタには64台のK20xが含まれるが、PEACH2ボードが接続されているCPUに接続されている2台だけがPEACH2経由の通信ができるようになっている。これはQPIを経由するPCIe転送の性能が低くて使い物にならないからであり、PEACH2の制約ではない。

なお、TCAシステム全体は64計算ノードで構成されており、これらの計算ノードはQDRのInfiniBandで接続されている。従って、サブクラスタをまたぐ通信は、このInfiniBandを使う。

TCAはDMAとPIOをサポートしており、最小レーテンシはDMAの場合は2μs以下、PIOは1μs以下となっている。PEACH2は4チャネルのDMAエンジンを持ち、各DMAエンジンは複数の転送をCPUの介在なしに連続して実行するディスクリプタのチェイニングをサポートし、2次元の行列の転送ができるブロックストライド転送もサポートしている。