東北大学国際集積エレクトロニクス研究開発センター(CIES)とキーサイト・テクノロジーは、次世代メモリの1つである「STT-MRAM」の測定技術を共同で研究し、その成果を基にキーサイトがSTT-MRAM測定システムの製品化することを決定したと発表した。製品のリリースは2016年初頭を予定しており、CIESにおける産学共同研究の成果に基づいた製品化発表となる。

CIESが運営する国際産学連携コンソーシアムでは、国際産学共同研究を実施することにより、集積エレクトロニクス機器の飛躍的省エネを実現する革新的な基盤技術群を創出することを目標として、7テーマの研究開発を推進している。7テーマのうちの1つである遠藤哲郎教授を代表とする「不揮発性ワーキングメモリを目指したSTT-MRAMとその製造技術の研究開発」においては、飛躍的な省エネルギーシステムを実現する不揮発性ワーキングメモリの実用化を促進し、低炭素・省エネルギー社会の実現に貢献することを目的とするスピントロニクス技術とシリコンCMOS技術の融合によるSTT-MRAMとその製造を、産学が連携して開発してきた。

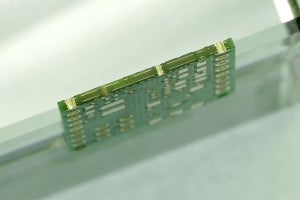

キーサイトは、この「不揮発性ワーキングメモリを目指したSTT-MRAMとその製造技術の研究開発」における測定技術開発分野に参画し、CIESが提供するSTT-MRAMを活用して、CIESと共にSTT-MRAMの測定技術に関して研究開発を行った。特に、STT-MRAMの測定技術に不可欠な高速な信号生成技術や高精度の測定技術等、さまざまな有用な評価技術を開発してきた。

今回のCIESとの共同研究を通して、高速信号生成と、高精度測定技術に一定の成果を得たことで、STT-MRAM測定システムを2016年初頭のリリースを目指して製品化することを決定したという。