OKIグループのプリント基板事業会社であるOKIプリンテッドサーキット(OPC)は12月24日、次世代スマートフォンなどで使用が予想される、端子ピッチ0.35mmで端子数1000ピンの次世代半導体に対応した最大板厚3.5mm(30層)のプリント配線板の量産技術を確立したと発表した。

狭ピッチ対応のプリント配線板製造技術としては、コア基板に配線層を1層ずつ積み上げていくビルドアップ工法が一般的だった。同工法では、隣接する配線層間のみの配線接続となり、多層化すると製造プロセスが複雑化するため、コストアップ、長工期化が問題で1000ピン以上の多ピン対応が困難であるとともに、多ピン化により増加した信号に対する電源・グランドの安定確保が大きな課題となっていた。これに対し、多数の配線層を一括形成し全層を貫通ビアで配線接続する貫通ビア工法は、プロセスがシンプルでビルドアップ工法に対して低コスト化・短納期化に有利だが、配線層積層時の層間ずれや極小径穴あけ精度に課題があり、貫通ビア形成時に穴位置がずれるため、狭ピッチ対応には適していなかった。

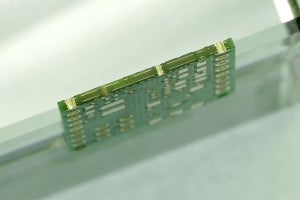

今回、OPCではこれらの既存技術の短所を補填し、最大板厚3.5mm(30層)の基材に0.35mmピッチで極小径(仕上がりφ0.10mm)の貫通ビア形成を実現する「FiTT(Fine pitch Through via Technology)工法」を開発した。配線層間ずれを40μm以内に抑える高精度積層技術、穴位置を製品に合わせμm単位で補正するシステム、およびドリル形状・穴あけ加工ステップの最適化による高精度穴あけ加工技術により、端子ピン数1000ピン以上に対応する高多層プリント配線板の量産を可能にしたという。同技術は、貫通ビア構造のため高多層でも電源供給、グランドの接続が安定的に確保でき、半導体の機能試験装置用基板に要求される高い信号品質を確保することができる。また、シンプルなプロセスのため、低コストかつ短納期での製造を実現する。

なお、同製品は半導体テスタ用ソケットボード市場に向けて、12月より量産を開始した。また、今後は0.30mmピッチ以下の次世代プリント配線板の開発を推進し、ニーズにマッチした商品の開発に積極的に取り組んでいくとコメントしている。