東芝は6月12日、基準クロックを標準CMOS回路で生成する高精度CMOS発振器を開発したと発表した。同発振器を用いることで、従来の水晶発振器の置き換えが可能となり、電子機器の小型化が実現するという。

詳細は、ハワイにて開催される「2014 VLSI Technology シンポジウム」で6月13日(現地時間)に発表される。

近年、電子機器の小型化が著しく進み、内蔵部品の小型化や削減への要求が増えている。それに伴い、発振器の小型化や内蔵化への要求も高まっており、超小型発振器に注目が集まっている。現在、広く用いられている水晶発振器は周波数精度に優れているが、発振周波数が水晶の物理的な大きさで決まるため、比較的大きなパッケージが必要となる。一方、CMOS発振器は小型化が容易だが、発振周波数の温度依存性が大きく、周波数精度が低い点が課題だった。

そこで今回、個別にCMOS発振器の発振周波数の温度特性を高精度に校正する技術を開発した。同校正技術により、水晶発振器に迫る±100ppm(0.01%)以下という周波数精度を持つCMOS発振器を実現した。また、従来の水晶発振器が決められた周波数のみ出力するのに対し、CMOSのデジタル演算能力を活かして、2MHz~40MHzの広い周波数範囲の中から、40Hzの非常に細かいステップで出力周波数を設定することも可能にした。

温度特性の校正は初期テストを行い、内蔵されたヒータと温度計を用いてチップ内で自律的に行われる。チップ温度を変更しながら発振周波数を自動計測し、各温度において必要な校正量をデジタル演算処理により求める。また、熱設計技術を駆使し、校正時における発振器周辺の温度の均一化を図ることで、高精度化を実現した。一方、実使用時にはチップ温度に応じた校正量がCMOS発振器に適用され、高い周波数精度を維持する。

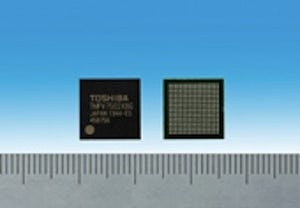

今回開発されたCMOS発振器は2~3年後の製品化を目指す。これにより、従来の水晶発振器の約1/3の小型化が実現する。さらに、MCUやASICなどのシステムLSIへの発振器の内蔵化も進めていくとコメントしている。