産業技術総合研究所(産総研)は6月9日、大規模集積回路(LSI)の消費電力低減に有効な、InGaAs n型MOSFETとSiGe p型MOSFETにより構成される3次元積層CMOSリングオシレータ回路を試作し、その回路動作に成功したと発表した。

同成果は、同所 ナノエレクトロニクス研究部門 新材料・機能インテグレーショングループの前田辰郎主任研究員らによるもの。詳細は、6月10~12日(現地時間)にハワイにて開催される「2014 VLSI Technology シンポジウム」で発表される。

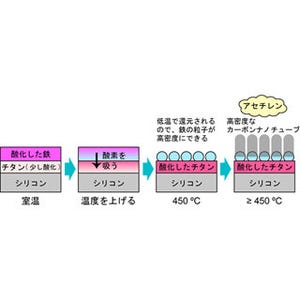

ポストシリコン材料と呼ばれるInGaAsやSiGeは、従来のLSIで用いられているSiに比べ、より低電圧で多くの電流を流すことができる。そのため、これらのポストシリコン材料を組み合わせたデュアルチャネルCMOS回路は、高速性などの性能を維持したままで、消費電力の低減が期待できる。今回、InGaAs-nMOSFETとSiGe-pMOSFETの双方に、高速性と省電力に優れた絶縁膜上の細線チャネル構造を採用して高性能化し、はり合わせによる3次元集積化技術を用いて、省スペース化されたCMOSリングオシレータ回路を作製した。さらに、この回路により低電圧動作(電源電圧0.37V)を実証した。

研究グループでは、今後もポストシリコン材料を用いた3次元積層CMOSの開発を進め、LSIのさらなる高性能、低消費電力化を目指す。また、はり合わせ技術を応用して、これまでシリコンでは困難だった発光・受光デバイスなどと3次元集積し、LSIとポストシリコンデバイスを1チップ化した、多機能集積化デバイスの開発を目指すとコメントしている。