産業技術総合研究所(産総研)は、電子機器の小型化、低消費電力化、高機能化に寄与する高密度部品内蔵インターポーザを開発したと発表した。

同成果は、同所 ナノエレクトロニクス研究部門 3D集積システムグループ(つくばセンター)の菊地克弥主任研究員らによるもの。

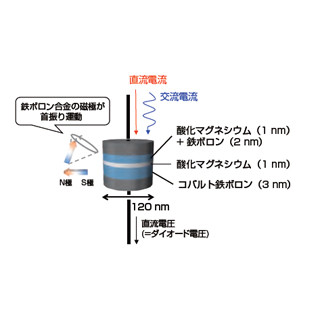

低消費電力で高速動作するLSIを実装するインターポーザでは、電源ネットワークを高周波帯域まで超低インピーダンス化し、電源ノイズの発生を抑制する必要がある。電源ネットワークのインピーダンスは、供給電圧と供給電流、最大リップル電圧の許容値から想定される値以下にする必要があるが、3次元積層集積LSIでは、10Gbps以上の高速信号伝送に対応するため、部品内蔵インターポーザを含めた電源ネットワークのインピーダンスを、直流(0Hz)~10GHz以上の広い周波数帯域で、0.1Ω以下にすることが求められている。この低いインピーダンスを実現するためには、インターポーザにこれまで以上の高密度でキャパシタを実装する必要がある。

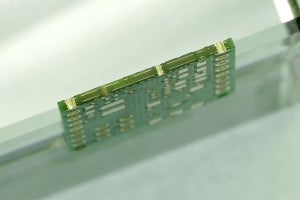

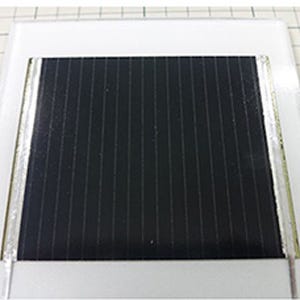

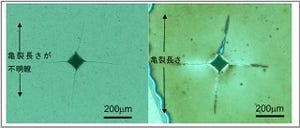

今回、研究グループでは、共同研究先の企業が開発した0.1mm間隔の狭間隔部品実装技術を、インターポーザ内層部に応用して0.4mm×0.2mmサイズのキャパシタを高密度に実装し、超広周波数帯域で超低インピーダンスの電源ネットワークを持つ高性能な部品内蔵インターポーザを開発した。そして、産総研が保有する評価システムを用いて、今回開発した部品内蔵インターポーザとシリコンインターポーザの電源ネットワークのインピーダンスを10Hz~10GHzの周波数帯域において測定した。その結果、開発した部品内蔵インターポーザがシリコンインターポーザと同様、低いインピーダンスになることが分かった。これにより、製造コストや信頼性の観点から、シリコンインターポーザに対して十分な競争力を持つと考えられるとした。

今後は、携帯端末機器メーカーや高性能半導体メーカーといった企業との連携を進め、高密度な部品内蔵インターポーザを用いたプロトタイプ機の開発を行い、実用レベルの応用技術開発を推し進めるとコメントしている。