東北大学は2月12日、最先端研究開発支援プログラム(FIRSTプログラム)「省エネルギー・スピントロニクス論理集積回路の研究開発」にて、共同事業機関および委託研究機関と進めた成果を発表した。

発表は、同大 省エネルギー・スピントロニクス集積化システムセンター(CSIS)の大野英男センター長らによるもの。詳細は、3月14日に東京国際フォーラムにて開催されるグループ最終成果報告会で発表される。

同プログラムは、高性能のスピントロニクス素子を開発し、それを搭載した革新的な省エネルギー論理集積回路を開発して、論理集積回路のパラダイムシフトを起こし、さらに、次世代半導体分野における日本の国際的な競争力の強化に寄与するとともに、低炭素・省エネルギー社会の実現に寄与することを目的としている。

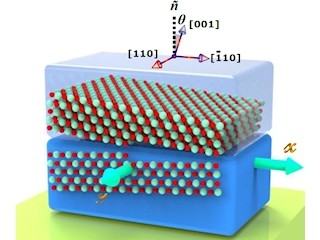

プログラムでは、"高性能スピントロニクス素子の開発"、"スピントロニクス論理集積回路の設計・試作・性能実証"、"スピントロニクス研究開発拠点の構築"の3つを具体的な目的としていた。"高性能スピントロニクス素子の開発"では、高い不揮発性と低消費電力を実現できるスピントロニクス素子である2重CoFeB-MgO界面構造を有する垂直磁気異方性磁気トンネル接合素子を開発した。これにより、直径20nmの磁気トンネル接合で不揮発性能(熱安定性Δ=58)、高トンネル磁気抵抗比(TMR比=120%)と低書き込み電流(書き込み電流値=24μA)を同時に得た。さらに、直径11nmの素子においてトンネル磁気抵抗効果と書き換えを行う基本性能を確認した。これは、磁気トンネル接合を利用したスピントロニクス素子を用いて、半導体メモリでは実現が困難であると予測されている20nm以下の技術世代で、不揮発メモリが実現可能であることを示したことになる。

"スピントロニクス論理集積回路の設計・試作・性能実証"では、性能実証を目的として素子数100万個を超える大規模なスピントロニクス論理集積回路群を設計、試作、評価した。対象となったは、高速CPUチップに混載される高速動作キャッシュメモリ、製造後にプログラム可能な汎用ゲートアレイ集積回路(FPGA)、データセンターのサーバ用の文字検索など検索に特化した専用集積回路、電池駆動センサ端末などで機器制御を行うマイコンである。不揮発記憶の特徴を有するスピントロニクス素子を搭載することによって、既存のCMOS集積回路に対して面積比×性能(遅延時間)比×消費電力比で1/64以下を実証した。

"スピントロニクス研究開発拠点の構築"では、スピントロニクス集積回路の設計基盤と製造基盤を整備し、スピントロニクス論理集積回路の設計・試作・性能実証の一連の研究活動を行うことができる研究拠点を構築した。さらに、国内外の研究者を招聘したスピントロニクス論理集積回路の共同開発を行い、同プロジェクトで開発した技術体系のデファクトスタンダード化に向けた取り組みを開始した。今後は、国家プロジェクトや産学連携をベースに、2012年10月1日に設立された東北大学 国際集積エレクトロニクス研究開発センター(CIES)と連携して研究開発を発展させ、実用化を目指した取り組みを進めていくとしている。