富士通研究所は1月14日、スーパーコンピュータ(スパコン)を利用して従来比3倍となる3000原子規模のナノデバイスにおける電気特性シミュレーションに成功したと発表した。

詳細は、応用物理学会の「Applied Physics Express(APEX)」に掲載された。

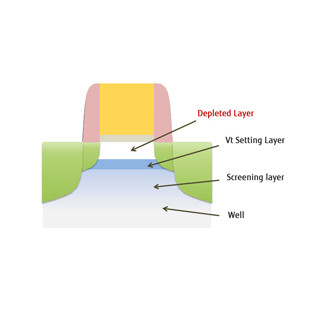

これまで、LSIをはじめとするシリコンデバイスは、プロセスの微細化によってデバイスの高速化や低消費電力化を実現してきたが、近年、その物理的な限界に近づきつつあると言われており、性能向上が次第に困難になってきている。そのため、新しい材料の導入や新しい構造のデバイス開発が盛んに行われている。

ナノデバイスの開発において、実験を行わずに計算機上だけで、正確な電気特性の計算ができれば、開発期間とコストを削減できる。それには、1つ1つの原子の振る舞いを正確に計算する第一原理計算による電気特性シミュレーションが有効となる。しかし、第一原理計算は膨大な計算が必要なため、電気特性予測に適用する場合、1000原子規模にとどまっていた。しかし、1000原子の規模では、電子の通り道であるチャネル部分だけの計算に限られ、電気特性に大きな影響を及ぼすと考えられる隣接する電極や絶縁膜との相互作用を取り入れるのに必要な原子、数千個規模のシミュレーションを実現することができなかった。

今回研究チームは、計算精度を保ちながら計算に利用するメモリ量を削減する計算手法と、スパコンの活用により、3000原子の大規模な構造でも第一原理計算による電気特性予測を可能にする技術を開発。電気特性シミュレーションでは、電気の流れを表すために基底関数の組を用いた。通常、基底関数の数が増えると計算結果の得られる電流値は正しい値に近づいていくが、一方で使用する計算メモリ量が増加する。今回、計算精度を保持しながら、計算メモリを約1/4、計算時間を約1/25に削減できる基底関数の組を発見し、これを用いることにより、利用メモリを汎用スパコンの許容メモリ以下にすることができ、3000原子規模のナノデバイスの電気特性を約20時間で予測することが可能になった。

シミュレーションの実施にあたって、北陸先端科学技術大学院大学と計算科学物質イニシアチブが開発した大規模並列化技術を用いた第一原理計算プログラムの「OpenMX」を利用した。同プログラムでは、原子の分割方法の工夫により、使用する通信量や計算メモリ量を削減できるのに加え、空間の分割方法の工夫により、第一原理計算で重要な高速フーリエ変換(FFT)の高速化が図られている。

これらの技術により、グラフェンと絶縁膜で構成された3030原子からなるナノデバイスの電気特性のシミュレーションが可能になった。

|

|

|

絶縁膜がある場合とない場合のシミュレーション結果。(左)グラフェンナノリボンチャネルと絶縁膜付シリコン基板で構成された3030原子からなるナノデバイスの計算モデル。(右)電気伝導シミュレーションにより得られたソース・ドレイン電圧が0.5V時のナノリボン当たりの電流 |

今回開発した技術により、3000原子規模の電気特性シミュレーションが実現できるため、部分間の相互作用まで取り入れたナノデバイス構造の電気特性を把握することが可能になり、新しいナノデバイス設計の実現に向けた研究が前進することとなる。また研究チームでは今後の計算機の性能向上に足並みを合わせる形でさらなる大規模並列化技術の開発を進め、より大規模で効率的な計算を追求していくことで、数年中にナノデバイス全体のシミュレーションを達成(1万原子規模)し、計算機上におけるナノデバイス設計の実現を目指すとしている。