東北大学は12月10日、線幅20nmの磁壁移動メモリ素子を作製し、良好な動作を確認するとともに、過去の報告値を1桁超下回る電力で磁壁移動による情報の書き換えが可能であることを実証したと発表した。

同成果は、同大 省エネルギー・スピントロニクス集積化システムセンターの大野英男センター長(同大 電気通信研究所 教授、原子分子材料科学高等研究機構 主任研究者、国際集積エレクトロニクス研究開発センター 教授兼任)らによるもの。京都大学 化学研究所の小野輝男教授らのグループと共同で行われた。詳細は、12月9~11日に米国ワシントンD.C.で開催される「International Electron Device Meeting(IEDM)」にて発表される。

"小さくすれば性能が上がる"という原理のもとで半導体論理集積回路は数十年に渡って目覚ましい発展を遂げてきた。しかし現在、この微細化が迎えつつある。これは、主に現在の半導体論理集積回路が電子の持つ電気的性質に立脚していることに起因している。このような中、注目されているのがスピントロニクス論理集積回路である。スピントロニクス論理集積回路は、半導体論理集積回路が築き上げてきた優れた特性を継承しながら、待機電力と動作安定性の問題が顕在化しつつある記憶機能に関して、電子の持つ磁気的性質(スピン)を活用した不揮発性スピントロニクス素子で置き換えられる。これによって、これまで通りの"小さくすることで性能を上げる"というスキームを継続できると同時に、スピントロニクス素子の持つ情報保持に電力が不要な不揮発性という特徴によって消費電力を劇的に低減することができる。

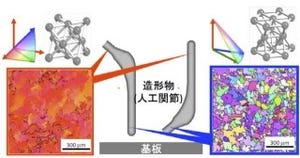

3端子型磁壁移動メモリ素子はスピントロニクス素子の1つの形態だが、高速・高信頼動作が可能なことから、従来の論理集積回路においてSRAMが担っていたようなキャッシュメモリやロジック周辺の一時記憶回路への適用が期待されている。これまで、線幅100nm程度の磁壁移動素子において、良好な動作や高い信頼性が確認されていた。

一方で、半導体論理集積回路の回路パターンの微細化は年々進行しており、現在は32~16nm程度が研究開発の最前線となっている。従ってスピントロニクス素子を最先端、および次世代の半導体集積回路に適用するためには、良好な特性を維持しながらこのような微細なサイズにまで縮小できること(スケーラビリティ)が求められるが、磁壁移動素子について、このような観点での研究は十分に行われてこなかった。

今回、研究グループは、様々な線幅の磁壁移動素子を作製し、磁壁移動特性や磁壁の熱安定性、および素子サイズ依存性を評価した。そして、これまでの報告を遥かに下回る線幅20nmの素子において、良好な動作を確認した。また、同素子が、デバイス特性の素子サイズ依存性の評価から、情報の書き換えに要する電流は微細化に伴いほぼ線形に減少する。情報の書き換えに要する時間も微細化に伴いほぼ線形に減少する。情報保持特性(熱安定性)は素子のサイズに関わらず十分な値を維持できる。書き換え誤動作確率についても素子のサイズに関わらず極めて低い値に抑えられるなど、優れたスケーラビリティを有していることを明らかにした。

得られた実験結果をもとに、情報の書き換えの際に1ビットの磁壁移動素子で消費されるエネルギーを見積もったところ、線幅が20nmの素子では1.8fJという値が得られた。これは、過去に報告されていたスピントロニクス素子での書き換えエネルギーの最小値90fJの1/50であり、SRAMの1ビットセルの書き換えエネルギーと同等に小さい値である。このことから、磁壁移動素子は待機時の消費電力だけでなく、動作時の消費電力という観点でも非常に有望な技術であることが分かった。

今回の成果は2つの意義を有している。1つは磁壁移動メモリ素子が最先端、および次世代の半導体論理集積回路との親和性に優れた技術であること。すなわち磁壁移動メモリ素子を混載したスピントロニクス論理集積回路では、"小さくすれば性能が上がる"という半導体回路の特徴を引き続き享受できる。もう1つは、書き換え消費電力が数fJと従来の半導体回路技術並みに小さいということ。これは磁壁移動メモリ素子を混載したスピントロニクス論理集積回路が、多くのアプリケーションに展開できる汎用性の高い技術であることを意味しているとコメントしている。