産業技術総合研究所(産総研)は12月10日、新構造の採用によって、従来より2倍性能を向上させたInGaAsトランジスタを開発したと発表した。

同成果は、同所 ナノエレクトロニクス研究部門 連携研究体グリーン・ナノエレクトロニクスセンター(GNC)の入沢寿史特定集中研究専門員らによるもの。東京工業大学 電子物理工学専攻の宮本恭幸教授、住友化学と共同で行われた。詳細は、12月9~11日に米国ワシントンD.C.で開催される「International Electron Device Meeting(IEDM)」にて発表される。

現在、スマートフォンをはじめとした電子機器の消費電力低減が求められており、搭載されるLSIには、個々のトランジスタに供給する電圧(電源電圧)を低くすることがこれまで以上に求められている。従来、電源電圧は徐々に下げられてきたが、近年、1V程度で飽和しつつあり、2016年の予測でも0.8V~0.6Vに留まる。この原因は、トランジスタ材料であるシリコン(Si)の物性や平面型のトランジスタ構造が限界に近づいてきたためである。これに対し、Siより電子の移動度の高いInGaAsなどのIII-V族化合物半導体を導入し、さらに、FinFETなど、立体的なゲート構造を採用して、より低い電源電圧を達成するといった取り組みが活発化している。このような中、GNCでは、LSIの低電圧動作を目指して、高移動度材料であるゲルマニウム(Ge)やInGaAsを用いたMOSFETの高性能化に関する研究開発を行ってきた。

通常、InGaAs基板の表面の面方位は(001)面だが、(111)A面を用いると電子移動度が高くなることが報告されていた。今回、研究グループではエピタキシャル成長時に(111)A面より出現しやすい(111)B面上の電子移動度が(001)面上より大きくなることを発見した。そこで、トランジスタの電流駆動力増大に有利な(111)B面の利用を、オフ時のリーク電流を抑制するための立体チャネル構造と組み合わせるため、三角形断面のチャネルを持つトランジスタを作製した。

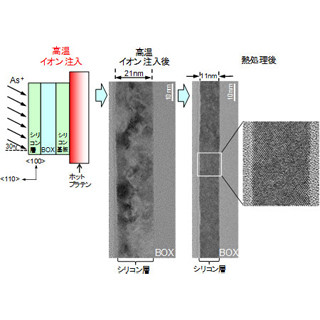

はじめに(001)InP基板の(001)面上にInGaAs薄膜をエピタキシャル成長させ、Si基板上の絶縁膜に貼り合わせた。さらに、塩酸によってInP基板だけを選択的にエッチングすると、通常の(001)表面を持つInGaAs薄膜が残る。この薄膜を微細な長方形断面の立体構造(InGaAs-fin)に加工した後、その上に、適切な条件でInGaAsをエピタキシャル成長させると、両斜面が(111)B面である三角形断面の立体チャネル構造が得られた。この時、下地の絶縁膜上にはInGaAsが成長せず、InGaAs-fin上にだけ選択的に成長させることができた。

当初、InGaAs-fin上にはリソグラフィやエッチング工程に起因する幅の不均一が存在したが、InGaAsの成長過程で平坦化されることも分かった。(111)B面上の成長速度が他の面上より遅く、(111)B面が広範囲に形成されるため、平坦化されると考えられる。なお、InGaAs-finの向きにより、表面が(110)面である類似の立体構造も形成されるが、(111)B面上の移動度の方が高かった。

この(111)B面三角形断面チャネル上にゲート絶縁膜(Al2O3)とゲート電極(TaN)を形成し、ニッケル(Ni)-InGaAs合金のソース、ドレイン電極を形成した。動作電圧相当の電子密度(~1×1013cm-2)では、従来の四角形断面チャネルのInGaAs-FinFET(従来型FinFET)の2倍の電子移動度が得られた。移動度が増大したため、チャネル長が300nmのトランジスタでは電流が72%増大した。これにより、同一の動作速度を得るための電圧を、従来型FinFETより低くできるので、電圧の2乗に比例する動作時の消費電力を大幅に低減することができる。例えば、電圧1V動作の従来型FinFETに比べて、消費電力を最大で57%低減できる。また、ノイズも従来型FinFETに比べて1/5程度に低減した。このような移動度の向上やノイズの低減は、(111)B面の高移動度と、表面平坦化の効果と考えられる。さらに、この表面平坦化は、トランジスタの電気特性のバラつき抑制にも寄与することが期待される。

今後は、p型トランジスタの高性能化に適したGeの立体チャネルトランジスタと組み合わせ、CMOS回路としての動作を検証していく。さらに、トランジスタ単体の性能だけでなく、Si-CMOS回路を上回る回路性能、あるいは低消費電力化を目指すとコメントしている。