富士通セミコンダクター(FSL)は12月10日、米SuVoltaからライセンスを受け共同開発した低消費電力化技術「DDC(Deeply Depleted Channel)」テクノロジを適用したロジック回路とフラッシュメモリセルとを混載して製造できる55nmプロセス技術を開発したことを発表した。

同成果の詳細は、12月9日より11日まで米国ワシントンDCで開催されている「IEEE International Electronic Device Meeting (IEDM) 2013」にて発表される。

不揮発性メモリは、データを保持するのに電力を必要としないという特徴から、IoT向け低消費デバイスでの活用などが期待されている。今回開発された技術は、その中の1種である「FLOTOX(FLOating gate Tunnel OXide) 構造」のフラッシュメモリと、DDCトランジスタ搭載回路を1チップ上に搭載可能とするもの。

FLOTOX構造のフラッシュメモリセルでは、浮遊ゲートに電子を注入する(書き込み) 、また浮遊ゲートから電子を抜き出す(消去)ことで、データの「0」と「1」を表現するため、注入された電子が浮遊ゲートから漏れ出すと正しいデータが保持できなくなる。中でも、書き込みと消去のサイクルを多数繰り返した後に漏れが発生する「シングルビット・チャージロス(SBCL)」は信頼性の面で最大の課題となっており、対応にはFLOTOX構造を形成する「STIコーナーラウンディング」や「トンネル酸化膜形成」工程において1000℃程度の処理が必須だと考えられていた。

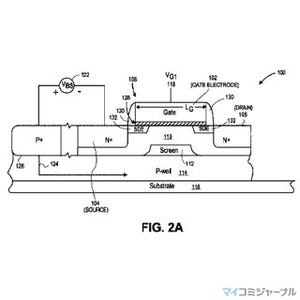

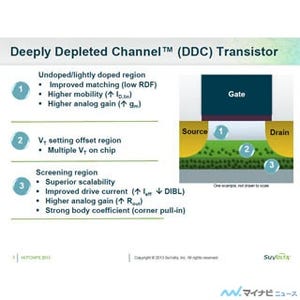

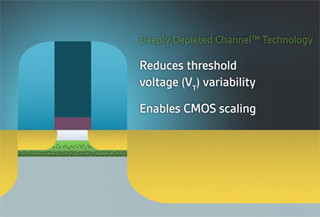

一方のDDCトランジスタは、ゲート電極の下に「Depleted Layer」という、不純物を極低濃度に保った層を形成する必要があり、そうした層の形成、保持には高温プロセスを用いることができないという課題があった。

そこで今回、同社では低温プロセスのみでFLOTOXを形成することを目指し、製造工程の見直しを実施。チャネル領域およびソース・ドレイン電極部分の不純物濃度分布が最適となるように調整を施した結果、DDCトランジスタに要求される特性を維持したまま、FLOTOX構造を形成できる処理条件を見出すことに成功したという。

実際に同条件を用いて、同社三重工場の55nmプロセスを用いて試作した評価用チップでは、フラッシュメモリ動作の初期特性が確認されたほか、書き込み・消去サイクル後のSBCL不良の発生がなく、信頼性についても問題がないことが確認されたとする。

また、最適化の過程において、SBCLが発生するメカニズムが、従来信じられていたトンネル酸化膜への電流ストレスではなく、ドレイン近傍で発生するホットホール(高いエネルギーを持った正孔)によって支配されている、という新たな知見を得ることに成功。これにより、今後の製造プロセスのさらなる最適化が進むことが期待されるという。

なお同社では今後も、機能・性能・コストを最適なバランスで実現する製造技術の開発を継続し、顧客製品の価値向上につなげていきたいとしている。