Intelは11月19日(米国時間)、米国コロラド州デンバーで開催されているスーパーコンピュータ(スパコン)最大の学会「Supercomputing Conference(SC13)」にて、ホストプロセッサ(CPU)として利用可能な次世代「Xeon Phi」(開発コード名:Knights Landing)が、標準的なラック・アーキテクチャに適合すること、またコプロセッサ上にデータをオフロードせずにアプリケーションを動作させる方法などを発表した。

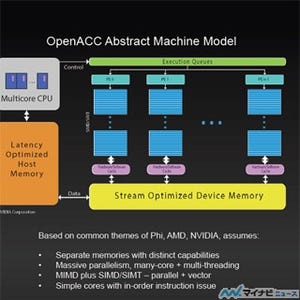

Knight Landingでは、パフォーマンスの最適化に向け、3種類のメモリ設定の選択肢が提供されることとなり、これによりシンプルな標準メモリ・プログラミング・モデルを活用することが可能になり、これらの方法により、プログラミングの複雑性が軽減されるとともに、データのオフロードが不要になりパフォーマンスが改善するため、メモリ、PCIe、ネットワークなどに起因する遅延を軽減することが可能になるとしている。

また、同社は富士通と、従来のコンピュータの電気配線を、Intelのシリコン・フォトニクス技術に基づいたイーサネットやPCIeのトラフィックを伝える光ファイバ網に置き換える可能性を持つ取り組みも併せて発表。これにより、Xeon PhiコプロセッサをホストとなるXeonプロセッサから隔離された拡張ボックスに組み込みながらも、機能はマザーボード上に組み込まれた時と同様に動作させることができるようになり、コプロセッサのさらなる高密度化の実現およびホストサーバに影響を与えることなくコンピューティングの規模を拡張することが可能になるとした。

さらに、Apache Hadoopに対応した「Intel HPCディストリビューション・ソフトウェア」も発表している。同製品は、Apache Hadoop対応「Intelディストリビューション・ソフトウェア」と「Intel Enterprise Edition of Lustreソフトウェア」を組み合わせたもので、大容量データの保存や処理などのエンタープライズ仕様のソリューションを提供となる。これにより、Lustre対応の高速な共有ストレージ上で直接MapReduceアプリケーションを設定変更せずに動作させることができるようになり、従来に比べ高速かつ高い拡張性を実現しながら、容易な管理を実現することが可能になると同社では説明している。