国立情報学研究所(NII)は10月8日、近年、量子コンピュータの実現に向けた基礎技術が実験的に成果を挙げてきていることを受け、現時点で最も有望とされる大規模量子コンピュータの方法である「誤り耐性(フォールトトレラント)量子コンピュータ」について、上層のアルゴリズムから下層の素子制御までのすべての技術レイヤを漏れなく統合する形で、実際の動作の流れに従って理論的にアルゴリズムの解析を行い、量子コンピュータの性能を総合的に評価することが可能な方法を開発したと発表した。

同成果はNIIの根本香絵 教授、Simon Devit 助教ならびにNTT物性科学基礎研究所のWilliam Munroリサーチスペシャリストらによるもの。詳細は10月3日付の英国科学誌「Nature Communications」に掲載された。

量子コンピュータの実現に向けた研究開発が各地にて進められているが、誤り耐性を有する量子技術は、誤り耐性を持たない量子技術に比べて多くの量子ビットを必要とすることが知られているが、そうした素子技術を結集して、大規模な量子コンピュータを実現した場合、実際にはどの程度の性能を発揮できるのか、といったことを具体的に示すことは難しかった。

量子コンピュータの性能を評価するためには、実際に情報の処理がどのような流れで行われているのか、という点まで含めて考慮する必要があるが、従来の古典テインコンピュータとは異なり、量子コンピュータではアルゴリズムから素子までのすべての技術レイヤを統合する事が難しいことから、システムとしての評価は不完全なものにならざるを得なかったためだという。

こうした課題を受け研究グループは今回、NIIが蓄積してきた量子コンピュータのアーキテクチャに関する知見とNTTが有する量子素子に関する知見を組み合わせることで、大規模な誤り耐性量子コンピュータにおける構成素子からアルゴリズムまでの技術レイヤを統合、量子コンピュータの性能を評価することを可能とする手法を確立したという。

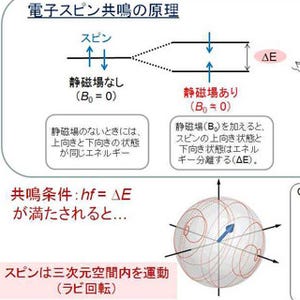

具体的には、最下層の構成素子から最上層のアルゴリズムまで、新たに導入すべきレイヤをも含めて特定し、大規模な誤り耐性量子コンピュータに不可欠なすべてのステップを明確化。技術レイヤの特定と統合は、構成素子に光と量子ビット(原子や固体中の2準位系)から成り立ち、光と量子ビットの合成系を制御することで、エンタングルメント(量子もつれ)を生成する「光モジュール」を3次元に規則的に配置し、「光モジュールネットワーク」を構成して、そのネットワークに「光モジュール上のスケジュール」で決められた通りに光子を送り込むことで、3次元の格子状にエンタングルした光子列を生成することで実現されたという。

これにより光子列は3次元トポロジカル量子計算のリソースで、一定の規則に従って光子を測定することで、「誤り訂正符号により保護された量子ビット(ロジカル量子ビット)」上で量子計算を進めることができるようになる。また、光モジュールネットワーク上に割り当てられたロジカル量子ビットは誤り訂正が可能だが、量子計算全体に誤り耐性を持たせるためには、誤り耐性のあるゲートの実装が必要となるため、量子コンピュータの「リソース・アロケーション」を決定し、ハードウエアのリソース配分を実施。さらに、誤り耐性のあるゲートの種類は限られているため、アルゴリズムからユニバーサル・ゲートセットへの分解により得られる「量子回路」を、誤り耐性のあるゲートセットへ分解して、「誤り耐性のある量子回路」を得ることに加え、ハードウエアのもつ制限を考慮してゲートの「スケジューリング」を行うことで、実行可能なゲート列の生成を実現したという。

各技術レイヤのリストは、他のスケーラブルな量子コンピュータの実装方式へも適用でき、実行可能性のチェックリストとして機能するほか、リソースやパフォーマンスのベンチマークへ用いることが可能であることから、実装しようとするアルゴリズムが、各素子に対してどのような振る舞いを具体的に要求しているのあを書き下すことが可能となり、これによりコンピュータのリソースと性能の評価を行うことが可能になったという。

実際にショアの因数分解について数値的な解析を行った結果、計算時間はモジュールの誤り率にあまり依存しないことが判明したという。

この結果、量子コンピュータのパフォーマンスは、素子の完成度の追及よりも、オペレ―ションをも含めたソフトウェアの工夫による高速化の方が有効であることが分かり、大規模な量子コンピュータを実現する上での(回路アーキテクチャなどの)ソフトウェア的な部分の重要性が示されることとなった。これは、ソフトウェア的な部分の改善を行うことで、実現すべき素子の技術レベルの低減化も可能であることを示唆するものであり、素子開発を行う実験チームへの新たな指針としても役立つものになるとの考えを示す。

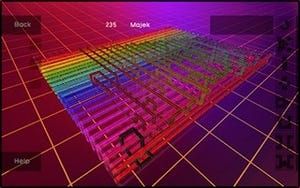

なお、研究グループでは、量子コンピュータの実現につながることが期待される、今回示されたソフトウェア的な切り口からの研究も今後進めていくとしており、その1つの手法として、トポロジカル量子回路の最適化問題をゲーム化した「meQuanics」を用い、オープンサイエンス的手法も取り入れて、研究を行っていくほか、素子開発チームと連携し、随時フィードバックを行っていく予定としている。