富士通と富士通研究所は10月8日、車載レーダーなどのミリ波送受信機へ適用可能な、低雑音な信号生成回路を開発したことを発表した。

同技術の詳細は、10月6日からドイツで開催されている国際会議「EuMIC 2013(European Microwave Integrated Circuits Conference 2013)」にて発表された。

近年、レーダーの高解像度化や無線通信の大容量化に向けて、周波数が数十GHz以上のミリ波を用いた送受信機の開発が進められているが、従来、ミリ波の送受信向け高周波ICには高価な化合物半導体が用いられているが、普及に向けた低コスト化、信号処理回路との一体化、高機能化などにはシリコン半導体での実現が必要とされているが、シリコン半導体では、低雑音なミリ波の信号生成が難しいという課題があった。

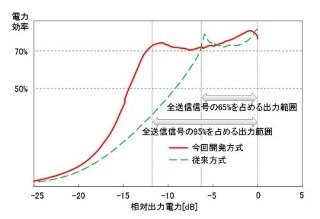

こうした課題に対し研究グループは今回、複数の位相差検出回路と遅延回路を直列に接続し、複数回比較処理を行う新しいアーキテクチャを開発。同回路では比較信号の周波数を高くし、さらに基準信号を分配して複数にすることで、1周期あたりの比較回数を増やすことができ、これにより生成する差信号の数が多くなり、位相差検出回路が発生する雑音に対して、比較結果の差信号を相対的に大きくできるようになった。その結果、位相差検出回路が発生する雑音の影響を少なくすることが可能となり、信号における雑音を従来回路に比べ約1/3(-5dB)に低減することに成功したという。

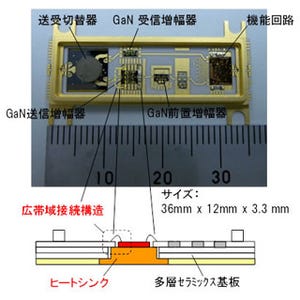

今回の成果を活用することで、車載レーダーなどのミリ波送受信機の高機能化・量産化が進むことが期待されるほか、雑音化による電力削減とレーダー部品点数の削減などの実現が期待されることから富士通では今後、これらの技術を活用した一体型ミリ波送受信ICモジュールの開発を進めていくとしている。