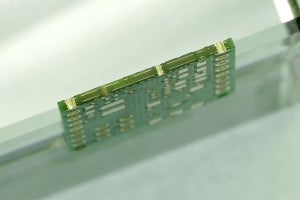

計測機器大手Agilent Technologiesの日本法人であるアジレント・テクノロジーは9月4日、差動ポータブルロジックアナライザ「Agilent 16850」シリーズを発表した。

ロジックアナライザを活用することによる、システムのデバッグや設計検証が加速している。通常、タイムアウト信号やエラーフラッグなど、トラブルの兆候が見られる箇所でトリガをかけて測定を行うが、根本原因となる箇所はトリガポイントよりもかなり前の段階で生じていることも多くなっている。「16850」シリーズの大容量メモリでの高速タイミングキャプチャを使えば、時間的にさかのぼり、トラブルの根本原因となっている箇所のデータを解析することができる。また、サンプリング分解能に優れているため、タイミングによる問題と機能面による問題との切り分けにも役立つ。これにより、デバッグや検証プロセスにかかる時間を短縮し、製品の迅速な市場投入につながるとしている。

フルチャネル使用時のタイミングスピードは2.5GHz、タイミング測定分解能は400ピコ秒、最大128MSaのメモリ搭載などにより、従来品に比べて、1.5倍以上高速なタイミングキャプチャを実現している。メモリ長も2倍となっている。ステートスピードは標準で700Mbps、オプションで1400Mbps。標準2MSaから最大128MSaの中で、必要なメモリ長オプションを選択することができる。ステートスピード、メモリ長とも、購入後のアップグレードに対応する。この他、1.4GHzのトリガ検出回路を搭載。高速回路の解析や、設定が難しい条件でのトリガ設定、トラブルの根本原因の迅速な発見に役立つという。

さらに、様々なバスや信号に対応した測定ソリューションとなっており、ロジックアナライザインタフェースと一体化したFPGAダイナミックプローブアプリケーションは、XilinxおよびAlteraのFPGAの内部信号を、大容量ステートキャプチャで簡単に捕捉することが可能となっている。

また、今回のロジックアナライザ向けとして、フライングリードプローブや汎用的なMictorコネクタ用プローブなど、低価格なプローブを新たに開発した。既存の90ピンコネクタプローブも利用できる。これにより、DDR BGAプロービングやDDRスロットインタポーザプロービングが可能となった。

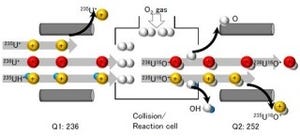

数多くの組み込みシステムでは、DDR2やDDR3メモリが利用されている。「16850」シリーズでは、ステートモードを利用して、メモリアドレスや制御バスのトレースを低価格で行うことが可能。さらに、メモリバスのデコードや、コンプライスンス試験やパフォーマンス解析ツールも利用でき、DDR2 1333およびDDR3 1333メモリのアドレスバス、制御バスのステート解析が可能となっている。

なお、価格は、34チャネルの「16851A」が144万2637円(税別)、68チャネルの「16852A」が184万6063円(同)、102チャネルの「16853A」が220万432円(同)、136チャネルの「16854A」が259万1607円(同)。すでに販売を開始しており、出荷開始は9月中旬を予定している。