東北大学は8月20日、強磁性細線中の磁壁をナノ秒電流パルスにより極めて高い確率で制御できることを実証したと発表した。

同成果は、同大 省エネルギー・スピントロニクス集積化システムセンター(CSIS)の深見俊輔助教、大野英男センター長(兼 同大 電気通信研究所 教授、原子分子材料科学高等研究機構 主任研究者)らによるもの。詳細は、英国の科学雑誌「Nature Communications」に掲載された。

次世代の半導体技術として、電子の電気的性質と磁気(スピン)の性質を融合した「スピントロニクス」を用いた論理集積回路の実現に向けた研究が進められているが、その核となる技術に、ナノメートルサイズの磁性体の磁気構造を電流によって操作する電流誘起磁化反転がある。強磁性細線中の磁壁を電流によって駆動する電流誘起磁壁移動はその1つで、既存の半導体集積回路との互換性に優れていることが知られており、電流誘起磁壁移動を利用した記憶素子をスピントロニクス論理集積回路に適用することで、デジタル機器の消費電力の低減が期待されている。

しかし、電流誘起磁壁移動を利用した集積回路を実現するためには、従来の半導体技術と同様にナノ秒領域においてエラーなく動作することが不可欠となるが、これまでの研究では、そうしたナノ秒領域での磁壁の確率的な振る舞いについて、十分な調査が行われていなかったという。

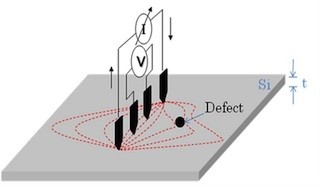

今回の研究は、そうしたナノ秒領域での調査を目的に行われたもので、具体的に、実験で用いられた試料の構造と実験の方法を模式的は示すと、Co/Ni積層膜を十字形状の細線に加工、その部分が磁壁のピン止め場所となり、そのような磁壁を有する細線に対して電流パルスを繰り返し導入することで、磁壁の脱出確率を測定したという。

|

|

|

図1 今回の研究で用いられた試料と実験内容の模式図。十字形状に加工されたCo/Ni積層膜からなる細線中にピン止めされた磁壁に対して電流パルスを導入したのが左の図。右の図は電流パルスの幅と振幅(電流密度)が十分大きいとき、伝導電子によって磁壁はピン止め位置から脱出できることを示している |

測定された磁壁の脱出確率が電流パルスのパルス幅と振幅(電流密度)を測定したところ、パルス幅を2ns程度まで短くしても、磁壁の脱出に必要な電流密度は増大していないことが判明した。2nsという速度は、従来の半導体ベースの集積回路と同等の書き換え動作速度と比較しても短いことから、電流誘起磁壁移動は高速性という点で十分な特性を有していると考えられるという。

|

|

|

図2 磁壁の脱出確率のパルス幅、電流密度依存性。(a)が実験結果で、(b)が計算結果。パルス幅が約2ns以上のとき、脱出に必要な電流密度のしきい値は一定となっている。また、計算結果と実験結果が良い一致を示している点も重要となる |

さらに、パルス幅を2nsで固定し、電流密度の大きさに対し、磁壁の脱出の失敗確率(エラーレート)を測定したところ、あるしきい値以上において電流密度の増加とともに急激に減少していることが確認され、これについて研究グループでは、電流誘起磁壁移動を利用した素子の書き換え誤動作確率が低く抑えられており、信頼性の高い記憶素子が実現できることを意味していると説明する。

|

|

|

図3 磁壁の脱出のエラーレートの電流密度依存性。(a)が実験結果で、(b)が計算結果。パルス幅は2ns。あるしきい値以上の電流密度において、エラーレートは急激に減少していることが分かる。なお、実験においては8.5x1011A/m2以上の電流密度では1万回の測定でエラーは観測されなかった。ここでも計算と実験は良い一致を示している |

また、得られた実験結果は、熱揺らぎの影響を考慮した理論計算によって良好に再現されることも確認されており、2つの実験結果に対する計算の結果ともに良い精度で一致していたことから、今回用いられた計算方法は磁壁の確率的な振る舞いを正確にモデル化できていると考えられ、今後の材料・素子開発の重要なツールとなることが期待されると研究グループは語っている。

なお、今回の研究にて、電流誘起磁壁移動を利用した記憶素子をスピントロニクス論理集積回路に適用することで、低消費電力でありながら、既存の半導体集積回路の持つ高速・高信頼動作という特徴を維持できることが明らかになったことから、研究グループでは、これによりスピントロニクス論理集積回路の実現に向けて大きく前進したと考えられるとコメントしている。