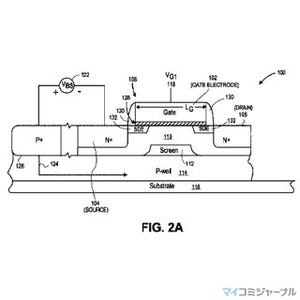

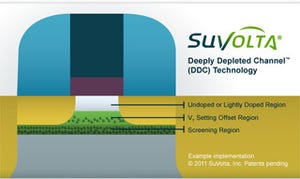

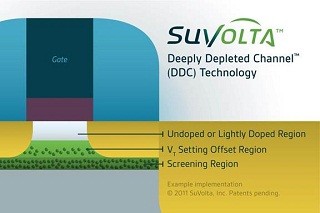

SuVoltaは7月23日(米国時間)、65nmプレーナ型のバルクCMOSプロセスに自社のトランジスタ技術「DDC(Deeply Depleted Channel)」を使って製造したARM Cortex-M0プロセッサを0.9Vで動作することを確認したと発表した。

これにより、従来の65nmプロセスを採用した1.2V動作のCortex-M0プロセッサと比べて、350MHz動作時で消費電力を50%低減できること、ならびに消費電力を同一にした場合、動作速度が35%向上することが確認されたという。また、電源電圧を1.2Vに引き上げた場合、動作速度は55%向上することも確認されたという。

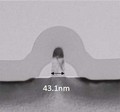

さらに同社は同発表と合わせて、台湾United Microelectronics(UMC)と28nmプロセスを共同開発することも発表した。

同プロセス技術は、UMCの28nm high-k/メタルゲート(HKMG)高性能モバイル(HPM)プロセスにSuVoltaのDDC技術を統合するもので、これによりリーク電力を下げ、SRAMの低電圧動作性能を上げることができるようになるという。

両社は早ければ今後数週間のうちに、こうした技術的なメリットを達成できる見込みとしており、既存の28nmプロセスに対し、以下の2つのオプションを提供することで、フレキシブルな対応を図っていくことが可能になるとしている。

1つ目のオプションは「DDC PowerShrink低消費電力プラットフォーム」で、すべてのトランジスタにDDC技術を適用させるというもの。2つ目のオプションは「DDC DesignBoosterトランジスタ交換」で、既存の設計データベースを元にトランジスタを部分的にDDCトランジスタに置き換えるというもの。例えばリーク電流の多いトランジスタをDDCトランジスタに置き換えることで、リーク電流を低減したり、SRAMのメモリセルトランジスタをDDCトランジスタに置き換えることで、性能改善が図られ、電源電圧を低減できるようになるとしている。

なおSuVoltaは、大手のファブレス企業やファウンドリとコラボレーションすることで、先端プロセスノード向け技術を着実に進展させていくとコメントしている。