東北大学は6月14日、グラフェンとSiテクノロジーとの融合デバイスの実現に向け、微細加工Si基板上へのグラフェンの位置選択的な結晶成長技術の確立に成功したと発表した

成果は、同大 電気通信研究所 吹留博一准教授らによるもの。同大 大学院工学研究科、および高輝度光科学研究センター(JASRI)と共同で行われた。詳細は、米国電気電子学会(IEEE)の主機関紙「Proceedings of the IEEE」に掲載された。

炭素の2次元物質であるグラフェンは、Siの100倍以上のキャリア移動度を有し、かつ、熱的・化学的にも安定な物質である。このため、 2020年頃に終焉を迎えるとされるSi集積回路に代替となる次世代デバイス材料の1つとして、全世界で開発競争が行われている。

研究グループでは、既存のSiデバイスとの融合を企図した、Si基板上へのグラフェン(Graphene-on-Silicon:GOS)の作製およびそのデバイス化の研究を行ってきた。GOS技術は、Si基板上に単結晶SiC薄膜を成長させ、この薄膜表面にグラフェンを形成していく。同技術は、成熟したSi技術の利用が可能なため、グラフェンの実用化を可能にする重要な技術という。加えて、Si基板の面方位を適切に選択することにより、グラフェンの物性の作り分けが可能なことが明らかにされており、同技術とSi微細加工技術の融合により、グラフェンの物性をナノスケールで作り分けが可能となることが期待されている。このように、GOS技術とSi微細加工技術との融合は、グラフェンの集積回路応用にとって重要なだけでなく、グラフェンの物性および機能の多機能化をナノスケールで可能にする点で重要となっている。

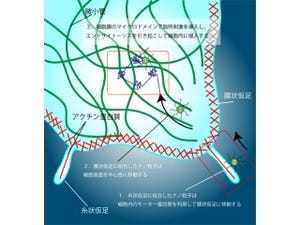

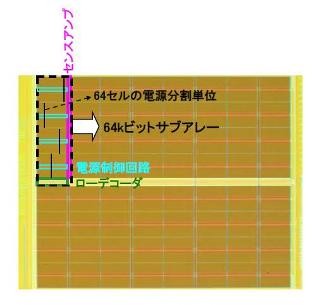

今回、図1のようなプロセスにより、Si基板の微細加工を利用したグラフェンのナノパターニングが試みられた。この試料の表面の状態がどのようになっているかを調べるために、NTT物性科学基礎研究所に設置されている低速電子顕微鏡を用いた顕微低速電子回折、および光電子顕微鏡(SPring-8設置)を用いた顕微X線吸収分光による解析が行われた結果、SiC膜中の欠陥密度の小さい領域Aの表面にグラフェンが形成されるのに対し、SiC膜中の欠陥密度の大きい領域Bの表面にはグラフェンが形成されないことが明らかとなった。この振る舞いは、領域BにおいてSi/SiC界面の荒れが大きいことに起因したSiC薄膜の欠陥密度の増加によるものと考えられるとのことで、研究グループでは、今回の結果は、欠陥密度の微視的な制御によって、狙った場所にのみグラフェンを成長させること(ナノパターニング)に成功した初めてのものだとしている。

|

|

|

|

図1 グラフェンのナノパターンプロセスの模式図 |

図2 低速電子顕微鏡および光電子顕微鏡によるグラフェンのナノパターニングの検証結果。SiCの欠陥密度が大きくなると、青点線矢印で示したピークが小さくなる |

グラフェンを用いた集積回路を作製する際には、例えば、素子分離プロセスなどにおいて、必要な箇所だけにグラフェンをナノパターニングさせる必要がある。このため、同技術は将来的なグラフェン集積回路の基盤技術となることが期待されている。

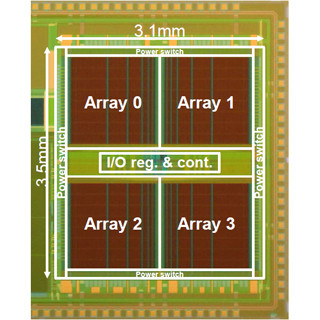

研究グループでは、今回の成果を発展させ、Si集積回路の主要技術であるイオン注入法で欠陥の導入を図るなど、よりスマートな方法によりSiC薄膜の欠陥密度を制御し、素子分離プロセスをナノスケールまで精密化することを検討している。さらに、MEMS技術との融合によるグラフェン機能のナノスケール多機能化の技術を融合し、多機能集積デバイスの実現を目指して研究を進めていくとコメントしている(図3)。