東北大学とNECは6月10日、スピントロニクス技術であるスピン注入磁化反転型磁気トンネル接合(Magnetic Tunnel Junction:MTJ)デバイスとシリコン技術を組み合わせ、ロジック混載用の1Mビット不揮発性メモリを開発したと発表した。

成果は、同大 省エネルギー・スピントロニクス集積化システムセンターおよび電気通信研究所 大野英男教授、同大 省エネルギー・スピントロニクス集積化システムセンターおよび工学研究科 遠藤哲郎教授らによるもの。内閣府の最先端研究開発プログラムにおいて、共同事業機関であるNECによる集積回路の試作協力を得て行われた。詳細は、6月11日~13日に京都市で開催される「2013 VLSI Technologyシンポジウム」で発表される。

論理集積回路はトランジスタの微細化とともに機能を増大させ、1つのシステムを1チップ化(システムLSI)することが可能となった。近年のシステムLSIでは、ダイに占める混載メモリの割合が増加してきており、現在の平均的なシステムLSIでは、チップの80%以上をメモリが占めている状況にあり、微細化による混載メモリの待機時電力の増加によってシステムLSI全体の性能が頭打ちになる状況に陥っている。

こうした状況の打開に向け、混載メモリを不揮発性化し、待機時における電力を削減する手法に期待が集まっている。この場合の不揮発性記憶デバイスとしては、CMOS回路との整合性、スケーラビリティ(微細化による性能向上) 、高速書き込み・読み出し性、および書き込み回数耐性などの観点から、MTJが最適なものと考えられているが、これまで提案されてきたMTJを使った大容量メモリは、いずれも混載メモリに要求される高速書き込みサイクルを満足するためには大電流を必要とするため、トランジスタサイズを大きくする必要があり、結果、セルサイズが大きくなってしまうため、実用的ではなかった。

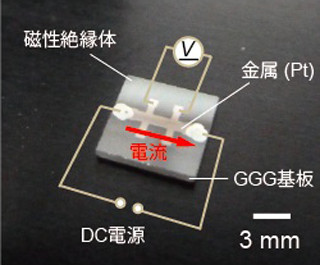

今回研究グループは、MTJとCMOS回路を同一集積回路上に混成した、いわゆるMTJ/CMOS混成回路において、高速書き込みサイクルが可能であり、セルの待機時電力ゼロを実現できる1Mビットロジック混載用メモリを開発することに成功した。これにより、高性能で低消費電力の不揮発性システムLSIの実現に向けて大きく前進したとしている。

また、システムLSIに使われている混載メモリとしては現在、スタティックRAM(6T-SRAM)が標準的に利用されているが、今回、研究グループでは、6T-SRAMと2個のMTJからなる6T2MTJ不揮発性メモリセルにおいて、6T-SRAMへの書き込みが終了しさえすれば、外部からのデータ入力が仮に遮断されたとしても、その6T-SRAMに書き込まれた新たなデータを使うことで、自動的に2個のMTJをスイッチさせることが可能である新たな書き込み方式も見出した。

ただし、MTJのスイッチングが終了した後も6T-SRAMへの電源を供給し続けた場合には、メモリセルでの消費電流が大きくなってしまうため、MTJスイッチ終了後に、64個まとめたセル単位(グレイン)で電源線(PL)を0Vに落とすように制御するタイマーを新たに設けることで、外部の書き込みサイクルが仮に短い時間内に終了したとしても、6T-SRAMのデータさえ反転していれば、MTJをスイッチするのに充分長い時間にわたり、グレインごとにPLを高電圧に保つことで、安全にMTJへデータを書き込むことを可能とした。

このMTJへのスイッチング動作は次のサイクルと時間的に重なっても、MTJへのスイッチはいわばバックグラウンドで実行されているため、次サイクルが読み出しであれ、書き込みであれ、問題なく高速にサイクルを続けることが可能だという。

実際に同6T2MTJセルならびにバックグラウンド書き込み方式を採用した1Mビットメモリを設計し、90nm CMOS技術と100nm MTJ技術を使い試作した結果、1.5nsの読み出しサイクルと共に2.1nsの書き込みサイクルを実現できることを確認。これは、これまでに報告されたMTJを使った不揮発性メモリとしては世界最高速の性能になると研究グループでは説明する。

なお、研究グループでは、今回の成果について、将来のローパワー不揮発性コンピューティング・システムで重要になる不揮発性混載メモリで課題であった書き込みの低エラー率化とその高速化をコンパクトなメモリセルサイズを保ったままで実現できることを示したもので、将来のシステムLSIの高性能化ならびに低消費電力化への道を切り開く一歩になるものとコメントしている。