東北大学とNECは、スピントロニクス論理集積回路技術を適用した検索用論理集積回路を試作し、その動作実証において、文字検索処理に必要な消費電力を1/100に削減することができたと発表した。

詳細は、6月11日~13日に京都府京都市で開催される「2013 VLSI Technologyシンポジウム」で発表される。

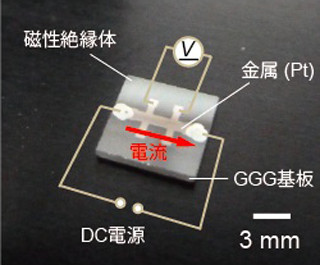

スピントロ二クス論理集積回路技術は、論理集積回路上のすべての回路を不揮発化することができるため、機器の低消費電力化に向けた技術として期待されており、東北大とNECもこれまで、同技術を用いて、汎用検索集積回路(TCAM)、画像処理プロセッサなどを試作し、これらの動作実証を行ってきた。

今回、研究グループは、これまでの研究開発の結果を活用して、文字検索システムに適用した場合に省電力性が得られる検索用回路技術を開発したほか、同技術を適用した小規模な検索用論理集積回路を実際に試作し、その動作実証において消費電力を1/100に低減できることを確認したという。

今回の検索用論理集積回路の特徴は2つ。1つは、要素回路に「多機能CAMセル」を新たに開発し搭載したこと。文字検索は、HDDなどの記録媒体中の索引に記憶されている文字列の中から、検索文字列と一致するものを探す手法で、検索用の集積回路であるCAMを用いて検索システムを構築した場合、1つの操作で膨大な数の文字列検索が可能になるとともに、従来の検索処理で行われている、DRAMとCPU間のデータ転送を伴う逐次的な処理をなくすことが可能となる。これらにより、高速に検索処理を実現できるとともに、DRAMとCPU間でのデータ転送に使用する消費電力をなくすことができるというメリットがあるが、CAMを使用した場合、検索文字列の長さに関係なく記憶されている文字列分すべての検索を行う必要があった。

今回開発された多機能CAMセルでは、短い検索文字列の場合、長い文字列との一致検出を行わないよう、検索不要であることを示す入力信号の組み合せ(パターン)を定めた上で、そのパターンが入力された時には、不要な文字列の検索を実行しない回路を実現したほか、索引中の、文字のない空白箇所については検索をしない(CAMセルが動作しない)パターンを設けることで、検索処理にかかる消費電力の削減に成功したとする。

また、今回の動作実証では、32文字までの索引語を4000語格納できる90nmのCMOS回路と垂直MTJを組み合わせた1Mビットの集積回路チップが用いられており、実際の動作電力は25.7mW、待機電力はほぼゼロとなることを確認したという。これは、従来のDRAMとCPUを組み合わせた検索処理と比べ、消費電力を1/100以下程度に低減できることを示している。

なお、研究グループでは今後、素子技術の進展により、ギガビット級のスピントロニクス論理集積回路が実現できるようになれば、今回の技術の実用化も近づくことになるとコメントしている。