パナソニックは6月10日、連続的に変化するアナログデータを安定的に抵抗値として記憶する強誘電体メモリスタを、CMOS回路上に形成することに成功し、同一回路上でデジタル信号をアナログデータとして扱うことを可能にしたと発表した。

同成果の一部は6月11日~14日の期間に開催される「2013 Symposia on VLSI Technology and Circuits」にて発表される予定。

強誘電体メモリスタは、従来の0と1で記憶するデジタルメモリに対し、0から1までの任意の中間値をアナログデータとして記憶・再生することできるため、多くの情報を記憶することが可能という特長を持っている。今回の成果は、「CMOS回路上に、シード層を介して強誘電体メモリスタを形成する結晶成長制御技術」と「入力されたデジタル信号をアナログ制御により演算した上で、結果を出力するハイブリッド回路設計技術」の2つを技術を用いることで実現したという。

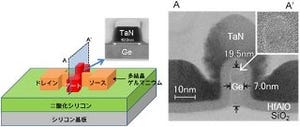

従来、CMOS回路最表面の絶縁膜は、隣り合う原子の配列が整合された状態では形成されていないため、直接CMOS回路上に強誘電体メモリスタを形成しても、強誘電体の原子の配列に歪みが生じ、アナログデータの良好な記憶・保持特性が得られなかった。今回の研究では、原子が規則正しく配列し、かつ原子間の距離が強誘電体に近い数値をもつ材料をシード層として選択することで結晶成長の方向を整えることに成功し、結晶性の良い強誘電体メモリスタの形成を実現したという。

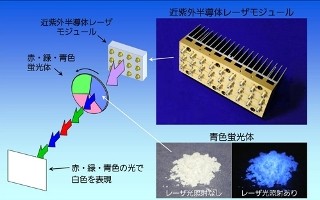

また、ニューラルネットワーク回路は脳の神経細胞の信号処理の仕組みをモデル化した回路であり、その信号処理は、複数の演算素子間がパルス信号と呼ばれるデジタル信号で情報をやり取りし、演算素子内部では、パルス信号を電流として用いたアナログ演算を行っていることから、CMOS回路と強誘電体メモリスタを組み合わせた回路では、これらの特徴を生かし、強誘電体メモリスタが入力電源なしに記録したアナログデータを安定的に保持するというデジタル信号をアナログ制御により演算し、その結果を出力することを可能としたシームレスなハイブリッド回路を実現したという。

同社ではこれらの技術を用いた回路を、電子回路上で「人の思考」の一部を再現するニューラルネットワーク処理に応用した場合、消費電力を従来比最大1/10に削減することが可能になるとする。

また、より多くの記憶情報に基づく、効率的な演算処理により、処理データ量が大きくなるほど、電力消費量の削減率を高めることができるようになることから、将来的には、脳の神経細胞の動きを模倣した、ニューラルネットワーク信号処理回路の複雑・高度化を実現することが可能になるとしている。