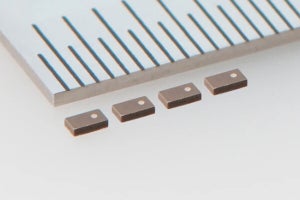

Cypress Semiconductorは3月20日(米国時間)、ARM Cortex-M0を搭載した「PSoC 4」アーキテクチャを発表した。

PSoC 4は、アナログおよびデジタルファブリックと、同社の静電容量タッチ技術「CapSense」、ARM Cortex-M0コアを統合したPSoCの新シリーズ。

150nAの待機消費電力を実現しつつ、従来ファミリに引き続きSRAMメモリやプログラマブルロジック、割り込みからのウェイクアップ機能を提供。ストップモードでは、ウェイクアップ機能を保持しながら消費電力を20nAに抑えることが可能なほか、Cortex-M0ベースのデバイスでは最大の動作電圧範囲を提供し、アナログおよびデジタル回路は1.71~5.5Vで動作する。

また設計は、同社の統合設計環境(IDE)「PSoC Creator」で行われ、あらかじめキャラクタライズされ量産使用が可能な「PSoC Component」と呼ばれるアナログおよびデジタルIPブロックを、1つのPSoCデバイスにドラッグアンドドロップすることでデザインが可能で、容易に差別化された製品開発が可能になる。

なお、PSoC 4ファミリの供給体制などの詳細については、2013年上半期に発表される予定。