CEVAは2月19日(米国時間)、ワイヤレス・ターミナル、スモールセル、アクセスポイント、メトロ/マクロ基地局など、高性能ワイヤレス・アプリケーション向けに「CEVA-XC DSP architecture framework」の機能強化としてDSPとマルチコア・システム・テクノロジ「MUST」を組み合わせたパッケージを発表した。

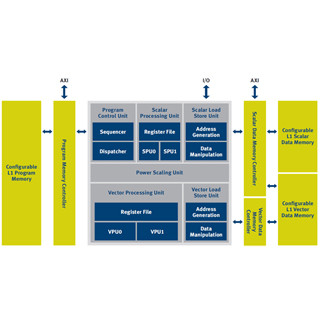

MUSTは、キャッシュベースのマルチコア・システム・テクノロジで、キャッシュ・コヒーレンシ、リソース・シェアリング、およびデータ管理を先サポート。CEVA-XCで利用できる最初の機能は、対称型および非対称型マルチコアプロセッシングのシステム・アーキテクチャで複数のCEVA-XC DSPコアへの統合をがサポートするというもので、マルチコアDSP処理に特化して設計された広範囲のテクノロジも同様で、以下の技術が提供されるという。

- タスクの共有プールを用いた動的スケジューリング

- ソフトウェア定義によるハードウェア・イベント・ベースのスケジューリング

- 共有リソース管理で駆動するタスクとデータ

- フル・キャッシュ・コヒーレンシを含む先進の階層メモリサポート

- ソフトウェア干渉のない先進の自動データ・トラフィック管理

- タスク認識に基づく特別な優先順位スキーム

また、ARMプロセッサおよび複数のCEVA DSPからなる先進マルチコアSoCの開発を促進するために、CEVA-XCアーキテクチャ・フレームワークへのサポートを強化し、ARM AXI4接続プロトコルやAMBA 4 ACE(AMBA Cache Coherency)を追加しており、これによりSoC設計におけるソフトウェア開発とデバッグ・プロセスがシンプルになり、同時にソフトウェア・キャッシュ管理のオーバヘッド、プロセッサ・サイクル、外付けメモリのバンド幅の削減が可能になるという。

さらに、LTE-Advancedおよび802.11acスタンダードなどで用いられるMIMO(Multiple Input Multiple Output)処理向けに、従来からある固定小数点機能に加えて、浮動小数点演算向けのサポートをCEVA-XCベクタープロセッサ・ユニットに追加した。これにより、すべてのベクター要素で浮動小数点演算がサポートされ、サイクルごとに最大32個の浮動小数点演算まで処理することが可能になるという。

このほか、低消費電力および高性能に向けたワイヤレス・システムの最適化に向け、コプロセッサユニット「TCE(Tightly-Coupled Extension:密結合拡張機能)」の包括的セットも発表している。これらのコプロセッサは、CEVA-XCと密結合するハードウェアを用いることで、より大きな性能を得ることが可能なモデム機能を実現することが可能になるとしており、以下の機能が提供される。

- MLD(Maximum Likelihood MIMO Detector)

- 3G ディスプレッダ・ユニット

- NCOフェーズ補正を伴うFFT

- DFT

- ビタビ

- HARQ結合

- LLR圧縮/展開

なお、これらの密結合の拡張は、DSPメモリとコプロセッサ間において独自に自動化された低レイテンシ・データ・トラフィック管理によって補完されることから、同社では、完全に統合/最適化されたモデム・リファレンス・アーキテクチャの一部として提供することで、カスタマは製品やインフラ、Wi-Fiアプリケーションなどの総電力消費の低減や開発コストとTime-to-Marketの削減が可能になると説明している。