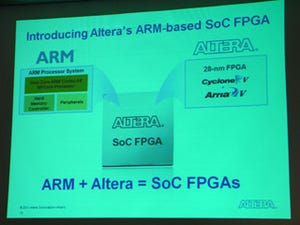

Alteraは12月12日(米国時間)、ARMと共同でAlteraのSoC FPGA向けにFPGA適合型デバッグ機能搭載「DS(Development Studio)-5エンベデッド・ソフトウェア開発ツールキット(Alteraエディション・ツールキット)」を開発したこと、ならびにデュアルコアARM Cortex-A9とFPGAロジックを1デバイス上に統合した「28nm SoCデバイス」の第1弾製品として11万LE相当の「Cyclone V SoC FPGA(5CSXA6)」のサンプル出荷を開始したことを発表した。

DS-5ツールキットとしては、はじめてのベンダ特化型のもので、これによりデュアルコアCortex-A9とAlteraのSoCデバイスにおけるFPGAファブリック間のデバッグの壁を取り除くことが可能となると両社は説明する。

従来、CPUとFPGAを用いた機器のデバッグには、CPU側とFPGA側それぞれ別々のツールを用いる必要があったが、AlteraのSoC FPGAの場合、FPGA内部にARMコアが搭載されており、従来ソリューションを用いる場合、CPUとFPGAをクロストリガし、ハードウェアとソフトウェアのイベントを関連付ける方法がないほか、CPU/FPGAの両方を同時に可視化し、制御する単体のツール/ケーブルがなかった。

今回のDS-5 AlteraエディションはAlteraのFPGAのみで使用可能なDS-5で、もともとのAltera側のデバッグ環境にDS-5を搭載する形で、FPGAに組み込まれたユーザーロジックのハードウェア部分と、CPUを一緒にデバッグすることができるようにしたもので、アプリケーションイベントとFPGAハードウェアイベントと関連付けられたCPUソフトウェアインストラクションの非介入型トレースにより、ARMコアおよびFPGA上でARMのデバッグ用トレースメモリやトレースイベント、デバッガ、トレース関連のIPである「CoreSight」の同時デバッグならびにトレースを可能とする。また、Streamlineに対応しており、ソフトウェア負荷およびCPU/FPGAのバストラフィック解析が可能となっている。

|

|

|

|

|

1つのデバイスに2つのデバッグツールを使うのはあまりに非効率的だということで、開発されたのが今回のDS-5 Alteraエディションとなる。DS-5のすべての機能が利用可能だが、Alteraのデバイスのみに適用可能にすることで、価格をかなり抑えることに成功したという |

||

なお、同ツールはAlteraの製品として提供され、ソフトウェア「Altera SoC Embedded Design Suite(Altera SoC EDS)」が2013年初旬より995ドルで、Cyclone V SoCを搭載さいた開発ボードをセットにした「Altera Cyclone V SoC Development Kit」が2013年4月より1495ドルにて提供される予定となっている。