産業技術総合研究所(産総研)は12月12日、チャネル長が3nmという極小トランジスタの動作実証に成功したと発表した。

成果は、同所 ナノエレクトロニクス研究部門 連携研究体グリーン・ナノエレクトロニクスセンター 右田真司主任研究員らによるもの。詳細は、2012年12月10日~12日に米国サンフランシスコで開催されている国際会議「2012 International Electron Devices Meeting(IEDM 2012)」にて発表された。

トランジスタの消費エネルギーを減らすために、材料や構造、動作原理といったさまざまな観点からの研究開発が世界各地で進められている。構造に関しては、プロセスの微細化が重要な設計指針となっており、現在20nm相当の寸法で作製した立体構造トランジスタで構成されるLSIが市場に登場してきた。また、研究開発では10nm以下に微細化したトランジスタの性能検証に関心が集まってきている。

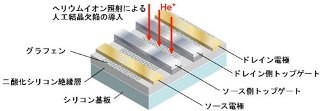

今回開発された技術は、既存の半導体製造方法を用いながら、ナノメートルスケールの構造制御技術および新しい接合技術を取り入れることによって実現した。

試作の手順はというと、絶縁膜の上にシリコン単結晶が貼り合わせてあるSOI基板を用いてトランジスタを作製。最初にアルカリ溶液でシリコン単結晶の限定された領域を溶解してV型の溝を形成。これはシリコンの結晶面によって溶解速度が大きく異なる性質を利用することで、特定の結晶面が残り、V型の溝が形成されることを利用したもので、溶解の温度や時間を調整することで、V溝の先端は曲率半径が3nmの鋭さになるという。この部分がトランジスタのチャネルになる。

一方、SOI基板の厚さについてはV溝の深さを精密に調整することで、チャネルの厚さが自在に設計でき、V溝構造を形成した後にゲート絶縁膜とゲート電極膜を堆積、パターン加工を行ってゲート電極を作製する。ソースとドレインに相当する部分にイオン注入を行い、最後に高温の熱処理で不純物の拡散を促進し、シリコン結晶全体にわたって不純物を均一に高濃度に行き渡らせるというものとなっている。

|

|

|

図2 開発されたトランジスタの試作手順。(a)アルカリ溶液でSOI基板を溶解し、V型溝を形成。(b)ゲート絶縁膜、電極膜を堆積。ゲートパターンを加工した後にイオン注入。(c)熱処理によって不純物を高濃度に均一に分布させて完成。V型溝の先端部分が曲率半径3nmの鋭さを有しており、トランジスタのチャネルとなる |

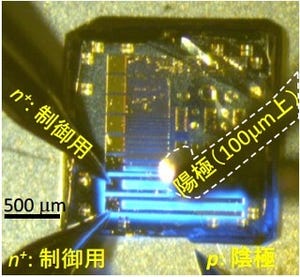

従来のトランジスタの作製方法では、不純物の拡散を抑制して濃度勾配を作り出し、PN接合を形成するが、微細化が10nm以下のトランジスタにおいて、PN接合の形成は困難となる。そこで今回、この課題を克服するために、PN接合を用いずにゲート電極の電界によって作り出されるエネルギー障壁だけでトランジスタを動作させる、新しい接合技術が採用された。図3は試作したトランジスタの断面構造を電子顕微鏡で観察したものだ。

図4はチャネル長3nmのトランジスタの電気特性。ゲート電圧を変化させることで、ドレイン電流を6桁以上にわたって変調することができることが確認された。ドレイン電圧の変化に対してもトランジスタとして正常な電流応答が確認されたという。

|

|

|

図4 試作されたトランジスタの電気特性。(a)ゲート電圧とドレイン電流の関係。図中の数字はドレイン電圧の設定値。(b)ドレイン電圧とドレイン電流の関係。ゲート電圧を0.2V刻みで最大2.0Vまで変化させて測定。これらの測定より、トランジスタが正常動作することが確認された |

トランジスタの高性能化には、チャネルの厚さも重要なパラメータの1つとなる。図5は、SOI基板のチャネル部分の厚さの効果を系統的に調べた結果で、厚さを1nm相当に薄くすることが、高性能化に必須であることが判明した。微細化が進行した極限では、構造をナノメートルの寸法で制御することが必要となることが示されたこととなる。

|

|

|

図5 チャネル厚さをナノメートルスケールで変化させたときの電気特性。SOI基板のチャネル部分の厚さを変化させて作製したチャネル長3nmトランジスタのゲート電圧とドレイン電流の関係。チャネル部分の厚さを1nm相当に薄くすることが、高性能化にとって必須となる |

図6は、今回開発されたトランジスタ内部の電子の速度を解析した結果。ソース端からドレイン端まで一定の速度で電子が流れていることが分かる。通常のトランジスタの場合、ソース端から注入された電子はチャネル内部での散乱を受けるために次第に速度が低下するが、チャネル長3nmのトランジスタでは、電子がほとんど散乱を受けずにドレインまで到達するため、速度が一定に保たれる。散乱を受けないということは、トランジスタ内部でエネルギーを損失しないことを意味する。このようなトランジスタを将来のLSIに用いることで、消費エネルギーの低減が期待できるという。

|

|

|

図6 チャネル内部の電子の速度の解析結果。ソース端から注入された電子は、速度が低下することなくドレインに到達している。つまり、大部分の電子は散乱を受けることなくチャネル内部を通過していることを意味する |

なお、研究グループでは、今回開発したトランジスタを元に、さらに低消費電力化が可能な新原理トランジスタの研究を発展させていく方針とコメントしている。