Intelサーバ全盛の時代に恐竜のようなメインフレーム? と思われるかも知れないが、IBMはメインフレームの改善を続けて、性能の向上と機能追加による適用範囲の拡大を行っており、今回の「zNext」にも注目すべき工夫が詰まっている。

メインフレームの売りは、企業などのバックボーンのシステムとして、一日24時間、週7日間、フル負荷で安定に動くという抜群の信頼度である。アムダールの法則で知られるG.Amdahl氏などが画期的なメインフレームであるSystem 360を1964年に完成して以来、50年近く開発が継続されている。その最新作が、Hot Chips 24でのプロセサの発表の前日の8月28日に発表された「zEnterprise EC12」である。

製品発表までこの名称は公開できないので、Hot Chipsでの発表資料はzNextという仮の名が使われている。この記事ではzNextと書く場合とzEC12と書く場合があるが、同じものである。ということで、Hot Chips 24では、IBMのChung-Lung(Kevin) Shum氏がzNextプロセサを発表した。

2000年以降のIBMメインフレームプロセサのクロック周波数とトランジスタ数の推移を次の図に示す。クロック周波数は2005年のz9から2008年のz10で大幅にジャンプし、その後のクロックの向上は緩やかになってはいるが、今回発表のzNextでは5.5GHzと商用プロセサではぶっちぎりの速さである。

また、トランジスタ数は急増しており、マルチコア、キャッシュの増大とマイクロアーキテクチャ的な性能向上が続けられている。

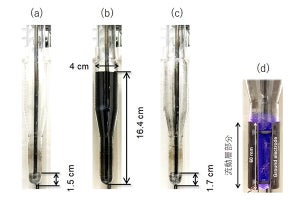

前世代のz196が45nm SOIプロセスで作られていたのに対して、zNextプロセサは製造プロセスを32nm SOIプロセスにシュリンクし、搭載コア数を4から6へと増やしている。また、3次キャッシュ量も24MBから48MBへと倍増している。

チップサイズは23.7mm×25.2mmで、今回のHot Chipsで発表されたプロセサとしては最大である。トランジスタ数は2.75Bで、富士通のSPARC64 Xの2.95Bには僅かに及ばないが、SPARC64 Xの2倍の48MBの3次キャッシュにeDRAMを使用しているからである。このチップサイズで5.5GHzのクロックであるので、恐ろしい消費電力ではないかと心配であるが、前の図では前世代と同じ程度のパワー制約で実現と書かれている。

z196からのクロックの向上は6%弱であるが、コアは第2世代のOut-of-Orderコアとなり、命令のフェッチからグルーピングといった命令供給系や、Out-of-Order命令実行系のキューのサイズの増加など、1サイクルあたりに実行できる命令数を増加させる改良が行われており、クロックサイクルの比よりも大きくコアの性能は向上している。また、コア数が1.5倍、3次キャッシュが2倍となっているので、チップあたりの性能は更に向上している筈である。

マイクロアーキテクチャのイノベーションとして、分岐予測の改良とキャッシュの改良について説明が行われた。前世代のz196については2年前のHot Chips 22で発表されたのであるが、その時の発表ではBTBとBHTを使っているという程度で分岐予測機構の詳細は発表されなかったが、今回の発表で5種類の予測テーブルを使う複雑な機構であったことが判明した。これが、zNextでは、次の図のようにメインの4KエントリのBTB(Branch Target Buffer)に24Kエントリと6倍サイズのBTB2が付加されてより多くの分岐先の命令がキャシュできるようになった。

これは元々のBTBが1次キャッシュとすると大容量の2次キャッシュを付けたということに相当する。しかし、これでは2次キャッシュであるBTB2のアクセスが遅いので、BTBのPre-BufferであるBTBPを設けている。また、1次キャッシュに相当するメインのBTBのアクセスを短縮するため、64エントリのFITを設け、最近使われた分岐先をここに覚えて置き、メインのBTBより速くアクセスできるようにしている。

これでもかと言う執念を感じる設計であるが、最近流行の性能/Wは改善されているのであろうか? まあ、メインフレームはメモリやストレージが大量に付き、システムとしての消費電力が大きいので、CPUチップの電力が多少増加しても、実行時間が短くなるほうがトータルの消費エネルギーが少なくなるので、ペイする設計ということであろう。

(後編に続く)

■Hot Chips 24関連記事

・【レポート】Hot Chips 24 - 富士通とOracleが次世代SPARCプロセッサを発表(中編) (2012年10月15日)

・【レポート】Hot Chips 24 - 富士通とOracleが次世代SPARCプロセッサを発表(中編) (2012年10月16日)

・【レポート】Hot Chips 24 - 富士通とOracleが次世代SPARCプロセッサを発表(後編) (2012年10月17日)

・【レポート】Hot Chips 24 - Intelの0.5V動作実験チップ「Claremont」 (2012年10月12日)

・【レポート】Hot Chips 24 - 次世代コアを並べて発表し、存在感を示したAMD(4) (2012年9月27日)

・【レポート】Hot Chips 24 - 次世代コアを並べて発表し、存在感を示したAMD(3) (2012年9月26日)

・【レポート】Hot Chips 24 - 次世代コアを並べて発表し、存在感を示したAMD(2) (2012年9月25日)

・【レポート】Hot Chips 24 - 次世代コアを並べて発表し、存在感を示したAMD(1) (2012年9月24日)

・【レポート】Hot Chips 24 - 学会初登場のIntelのメニーコア「Xeon Phi」(後編) (2012年9月19日)

・【レポート】Hot Chips 24 - 学会初登場のIntelのメニーコア「Xeon Phi」(前編) (2012年9月18日)

・【レポート】Hot Chips 24 - 乾いたタオルを絞るIvy Bridgeの省電力技術 (2012年9月7日)

・【レポート】先端プロセサの発表が盛りだくさん - Hot Chips 24が開幕 (2012年8月28日)