性能と電力効率を改善したJaguarコア

AMDは高性能のハイエンド用のBulldozerファミリと低電力で小型機器用のCatファミリの2種類のコアを開発している。今回発表のJaguarコアは、Bobcatに次ぐCatファミリの第2世代プロセサコアである。

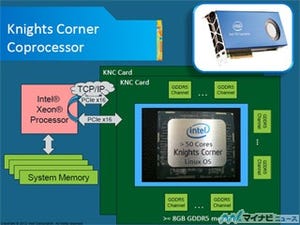

Jaguarコアを開発するにあたり、Bobcatに比べて性能と電力効率を改善することが第1の目標であり、第2の目標はIntelのSSE4.1、4.2、AES暗号、256bit SIMDのAVXなどの新命令に追随して機能レベルを上げること、第3の目標は別の半導体メーカーや異なる半導体プロセス世代での製造を容易にするプロセスポータビリティを上げることであったという。

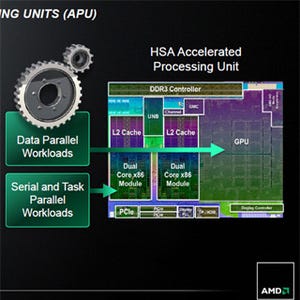

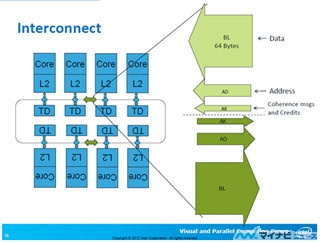

BobcatではコアとL2キャッシュがペアになっていたが、これをJaguarでは4コアと4バンクで2MBのL2キャッシュを一組としてCompute Unit(CU)という単位にまとめた。4コアで見るとL2キャッシュの合計の容量はBobcatと同じであるが、コアを止めてC6ステートにした場合、Bobcatではコアに付属する512KBのキャッシュも使えなくなってしまうが、Jaguarの場合は残るコアで2MB全体を使うことができ、コアあたりのキャッシュ量が大きくなるので性能が上がるというメリットがあるという。

次に示すJaguarコアのブロックダイヤは、Bobcatのものとほとんど同じであるが、それぞれのブロックには種々の改良が施されている。

プロセサのフロントエンドは、32KB 2wayの命令キャッシュを持ち、2命令の並列デコードを行う点はBobcatから変わっていないが、4個の32バイトのループバッファが設けられた。命令ループがこの中に入っていれば、命令キャシュを読まなくて良いので消費電力を低減する効果がある。また、命令キャッシュのプリフェッチも改良している。

そして、整数命令の実行部では、ハードウェアの割り算器が新設され、CRC32/SSE4.2などの命令を実行するユニットが追加されている。

浮動小数点演算部では、AVX命令をサポートするため、Bobcatでは64ビット幅であった演算器を128ビット幅に拡張し、4個の単精度の乗算と加算、あるいは1個の倍精度乗算と2個の倍精度加算が並列に実行できるようになった。また、この128ビットの演算器を2回使って256ビット長のデータを扱うAVX命令をサポートしている。細かいところでは、レジスタにゼロを入れるケースの処理の改善、浮動小数点レジスタのアクセスを2サイクルにしてクロック向上の制約にならないようにするなどの改良が行われている。

そして、ロード/ストア部では、ロード/ストアキューを改善し、Out-of-Order実行性能を改善する種々の改良を行い、浮動小数点ユニットへのデータパスの幅を128ビットと倍増している。これは浮動小数点演算ユニットが128ビット幅になったことに対応するもので、浮動小数点演算性能の向上に効果がある。

次の図はBobcatとJaguarのフロアプランの図であるが、不規則な形状の部分は自動配置配線で作られた部分で半導体プロセスが変わっても、新しいプロセスに対応したゲートライブラリを使ってCADで配置配線をやり直せば良い。プロセスのポータビリティという点では人手で頑張って設計するカスタムマクロを何種必要とするかが問題で、Bobcatではプロセサコアで7種、L2キャッシュで2種、クロック系で3種の合計12種のカスタムマクロの設計が必要であったのに対して、これをJaguarでは、プロセサコア部で3種、L2キャッシュ、クロックは各1種で合計5種に削減して移植性を高めたという。

使用する半導体プロセスがBobcatは40nmでコア面積が4.9平方mm、Jaguarは28nmプロセスでチップ面積が3.1平方mmであり、40nm→28nmの比率で考えると、JaguarはBobcatと比較して2割程度物量が増えていると思われる。

そして、BobcatからJaguarへの設計の改良を示すものとして、次のスライドを示した。

コアが動作を止めているHALT状態では、Bobcatのクロックゲートの効率は91.8%であったのに対してJaguarでは98.8%と改善しており、HALT時のダイナミックな電力消費は大幅に減少していると考えられる。また、アプリケーションを動作させた場合は、BobcatのIPC(サイクルあたりの平均実行命令数)は0.95であるのに対して、Jaguarでは1.1となっている。これがどのようなアプリケーションであるのかは明示されていないが、クロック周波数が同じとすればIPCに逆比例で実行時間が短くなり、消費エネルギーも実行時間に比例して低くなる。また、アプリケーション実行時のクロックゲートの効率もJaguarの方が高く、この点でも電力が減っていると考えられる。

そして、これらの設計改善により、典型的なプログラムの実行時のIPCは15%以上改善し、クロック周波数も10%以上向上し、新規命令の追加、異なる半導体プロセスへの移植性についても改善され、設計目標を達成したと結んだ。