STMicroelectronicsとCadence Design Systemsは5月31日(米国時間)、STがCadenceの支援を受けてミクスドシグナルSoC設計を実現するカスタム・アナログおよびデジタル設計向けメソドロジを組み込んだ20nmプロセスでのテストチップをテープアウトしたことを発表した。

共同で、20nmプロセス向け基礎IPおよびSKILLベースのPDK(Process Design Kit)を開発したことに加え、設計、インプリメンテーションおよびサインオフを実現するためのテクノロジを共同で開発し、Cadenceの設計プラットフォーム「Encounter」および「Virtuoso」を使用したメソドロジに適用することで実現したという。

具体的には、基礎IP、PLLおよびビデオD/Aコンバータ(DAC)を含むカスタムIP設計開発にCadenceのVirtuoso Layout Suiteを使用して自動レイアウト生成を行ったほか、高精度な結果を確保するため、設計者はModgens、制約およびスペース・ベースの配線などの先進的な機能を実現する20nm PDKを使用したという。

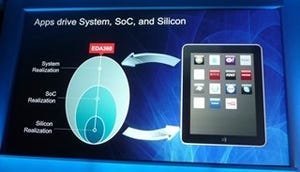

また、Encounter Digital Implementation(EDI)Systemがテープアウトに向けて、配置、最適化、および配線を行う際の20nmプロセスによる要求事項を処理し、20nmでのフィジカル・インプリメンテーションの機能を提供したとしている。