早稲田大学(早大)大学院情報生産システム研究科の後藤敏教授、周大江次席研究員らによる研究グループは、スーパーハイビジョン(8K4K)向けビデオ複合LSIの開発に成功したことを発表した。同成果は上海交通大学の協力によるもので、2月19日(米国時間)より、米サンフランシスコにて開催されている国際固体回路会議「ISSCC 2012(International Solid-State Circuits Conference,2012)」にて2月21日(同)にて発表される予定。

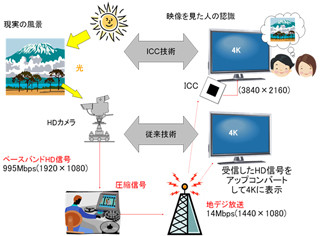

ビデオデータは解像度の向上とともにデータサイズも増加しているため、一般的には1/10~1/20程度の圧縮処理(符号化。エンコード)を行い、データの転送後、各機器にて伸長処理(複合化。デコード)を行うことで、データを復元して表示されている。ハイビジョン画像の圧縮方式としてMPEG-2が世界的に標準規格として使われてきたが、近年では圧縮度を約2倍に向上させたH.264規格も使用されるようになりつつある。この背景として、フルHD(1920×1080)の画像から、4K2K(4096×2160)のウルトラハイビジョン、そしてさらに高精細なスーパーハイビジョン(7680×4320)の開発も進められつつあり、こうした高解像度かつ巨大なデータ量を速やかに転送することが求められるようになってきているということがある。

こうした動きを受けて研究グループは今回、スーパーハイビジョン用ビデオ複合LSIを開発を行った。具体的にはフルハイビジョンと比較し、スループットとして32倍の高速性を達成する必要があり(2K1K@30fpsから8K4K@60fpsへ)、そのためにはDRAMバンド幅は32倍以上、演算量も32倍向上させる工夫が必要となることから、画像フレームを並列するして処理する方式を導入し、複合処理を2並列、エントロピー処理を4並列化することで最大スループット2Gpixel/sを実現したほか、データ転送量の削減を図るため、2レベルキャッシング、参照フレーム同期方式などの技術を開発、搭載することで外部DRAMとデコーダエンジン間の転送量を従来開発品比(4K2K@60fps)で24%削減(8K4K@60fps時)した。

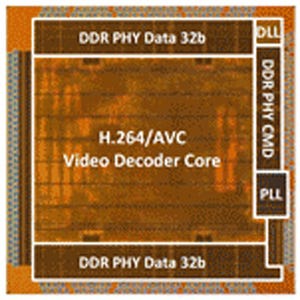

また、採用プロセスはSemiconductor Manufacturing International(SMIC)の65nm LPプロセス(9層Cu、標準シャトルサービス)を採用し、ロジック規模は130万ゲート、80KBのメモリを実現(ダイサイズは4mm×4mm)。外部DRAMはDDR2 400Mbps 64ビット品を採用し、ビデオフォーマットにはH.264 HP/MVCを、ビットレートはハイビジョンの20Mbpsから40倍となる800Mbpsに対応したほか、消費電力は8K4K@60fps時で従来品比で42%削減(スケーリング比)となる410mWを実現したという。

SMICの65nm LPプロセスを採用した理由について後藤教授は、「大学という立場として、まずはコスト。そして65nmプロセスが安定しているということと、最先端の40nmや32/28nmプロセスなどを用いなくてもデコードが可能であるという実証の意味合いもある」と説明する。また、今回、外部メモリにDDR2を用いており、よりバンド幅の広いDDR3を使わなかった理由としては「組み込みにおける取り回しのしやすさとコスト」とのことで、現在、世界的に話が進められている次世代標準の中で120fps化という議題についても、「もう1つ並列化処理を増やせばおそらく対応可能だと思うが、並列化といっても、できない部分とできる部分の仕分ける作業のチューニングや、単に並列度を増やしても性能はリニアに向上しないため、その解決策を模索していく必要がある」とした。

なお、今回のデコーダチップ開発はあくまで8K4Kのデコードが1チップでできるということの技術実証であり、仕様変更などの可能性がある現時点での半導体メーカーへの技術移管を行う予定はないとのこと。今後は、エンコーダチップの開発や策定が進んでいるH.265に対応したチップの開発を進めて行きたい研究グループではコメントしている。