富士電機は12月22日、業界最高レベルの低損失を実現したMOSFET「Super J-MOSシリーズ」を発売した。同製品は、新たに開発した低オン抵抗特性を持つSJ(Superjunction)構造を採用することで損失の低減を実現しており、これにより、サーバなどの情報通信機器の電力変換効率を向上させ、消費電力を削減することが可能になるという。

今回開発したSJ構造は、 MOSFETのドリフト層をp型領域とn型領域とが交互に並んだ構造に置き換えたもので、n型領域の不純物濃度を高くすることが可能で、抵抗値を低減を図ることが可能となる。 従来のプレーナ構造のMOSFETでは、高抵抗のn型層に電気的に絶縁された領域(空乏層)を伸ばすことによって耐圧を確保していたため、オン抵抗を一定値以下にはできなかった。SJ構造は、n型領域にp型領域を形成することで、縦方向だけでなく横方向にも空乏層を伸ばすことができるため、n型層の抵抗を下げても耐圧を確保することが可能である。

このため、同製品はオン抵抗を従来品比70%減を実現し、業界最高レベルの低損失を達成した。また、同社のスイッチング損失低減技術と組み合わせることで、素子のトータル損失も同14%低減することに成功している。

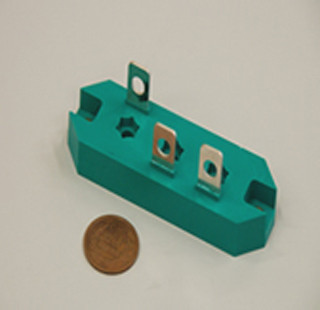

なお、同シリーズは、まず定格電流20A品の発売を開始し、2012年4月には同30A品、47A品、68A品の発売を予定している。