産業技術総合研究所(産総研) ナノエレクトロニクス研究部門 シリコンナノデバイスグループの松川貴 主任研究員、昌原明植 研究グループ長らの研究グループは、14nmプロセス世代の立体型トランジスタ(Fin-FET)のオン電流バラつきの主要因を解明したことを12月5~7日まで米国にて開催された半導体の国際会議「IEDM 2011」にて発表した。

半導体のプロセス微細化競争は、今や22nmや20nmプロセスへと突入しようとしている。しかし、2017年以降に市場投入が見込まれている14nmプロセス世代のトランジスタ技術では、その寸法の小ささから素子間の特性バラつきの問題が顕在化してくると考えられ、製品の歩留まり低下などが懸念されている。特にシステムLSIやマイクロプロセッサの50%以上の面積を占めるSRAMは、最小寸法のトランジスタを多用するため特性バラつきの影響を受けやすいことから、特性バラつきの少ない微細トランジスタの開発が求められてる。

産総研では、これまでも3次元立体構造にしたFin-FETの研究を行ってきており、2003年には素子特性を電気的に制御するための端子が付加された4端子型Fin-FETを提案したほか、2008年にはFin-FETにおける新たな特性バラつき要因として、金属ゲート電極材料の物性のバラつきを提唱、さらには2010年に、その物性バラつきの低減を可能とするCMOSプロセスの提唱などを行ってきた。

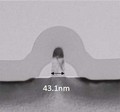

今回、ゲート長80nm、Fin厚さ25nm、48素子のFin-FETについて、電気的特性バラつきの評価を行った。集積回路の性能に直結するオン電流バラつきの主要因としては、従来、しきい値電圧バラつきが指摘されているが、しきい値電圧バラつきを揃えても、相互コンダクタンスバラつきによりオン電流バラつきが発生していることが確認された。

そこで、電気的特性より、しきい値電圧バラつき、寄生抵抗バラつき、相互コンダクタンスの3つのパラメータのバラつきを評価したところ、3つのパラメータ同士の相関、それぞれのオン電流との相関、素子寸法との相関を詳細に解析し、オン電流バラつきへの3つの独立したバラつき要因の寄与率と素子寸法縮小による増加傾向予測を得ることができたという。

この結果、しきい値電圧バラつきの寄与がゲート絶縁膜厚の縮小により低減できるのに対し、相互コンダクタンスバラつきは素子微細化による低減が困難であるため、さらなる素子縮小に伴い重要な要因として顕在化し、14nmプロセス世代では、相互コンダクタンスバラつきが、オン電流バラつきの主要因となることが予測されるという結論に至ったという。

さらに、通常の加工技術(ドライエッチング技術)でFinチャネルを形成したFETと、産総研で開発されたナノウェットエッチング技術で形成したFETについて相互コンダクタンスバラつきを測定し、相互コンダクタンスバラつきに関するPelgromプロットを行った(図4)。

同プロットは、トランジスタ特性バラつきの指標として広く使われており、横軸はゲート面積の平方根の逆数、縦軸は相互コンダクタンスのバラつき割合(標準偏差/平均値)を示している。プロットの傾きAGmは、ゲート寸法の縮小に対するバラつきの増加率で、このAGmが小さいほど特性バラつきが小さく抑えられることを示す。また、ナノウェットエッチング技術によるシリコンFinチャネルの高精度な加工により、相互コンダクタンスバラつきが低減されることがわかった。

このナノウェットエッチング技術による相互コンダクタンスバラつき低減のメカニズムから、実測された相互コンダクタンスバラつきの要因をさらに解析した結果、移動度バラつきが主要因であることが判明した。移動度はチャネル中でのキャリアの散乱頻度により決まる。通常のドライエッチング技術によるFin加工では、レジストの凹凸(ラフネス)を反映してFinの側面にも凹凸が生じる。また、加工の際にプラズマによってFinチャネルにダメージや欠陥電荷が発生する。これらはキャリアの散乱体として作用して移動度を減少させるが、従来の加工技術では素子間に散乱体の密度のバラつきが生じて、結果的に移動度のバラつきを引き起こす。一方、ナノウェットエッチング技術による加工では、Finチャネルへのダメージがなく、また、Finの側面は極めて平滑となるため、散乱体の密度が低く抑えられ、移動度のバラつきや、それによって生じる相互コンダクタンスバラつきが抑制されていると考えられるという。

さらに、14nmプロセス世代Fin-FETのオン電流バラつきと、各要因の寄与を予測した結果を見ると(図6)、通常のドライエッチング技術を用いてFinチャネルを作製した場合、相互コンダクタンスバラつきが主要因となり、結果として大きなオン電流バラつきが発生するが、ナノウェットエッチング技術を用いて高精度にFinチャネル加工を行うと、相互コンダクタンスバラつきが低く抑えられ、オン電流バラつきが低減することが予測された。 研究グループでは今回の成果が、14nmプロセス世代以降で深刻になるトランジスタ特性バラつきの解決案を提示するものであり、ひいてはSRAMをはじめとする集積回路の歩留まり低下の解決への道筋を示すものとなるとの期待を示しており、今後、Fin-FETを用いた集積回路を作製し、回路レベルでの歩留まり向上の実証を目指す計画としている。