富士通セミコンダクター(FSL)とSuVoltaは、SuVoltaの「パワーシュリンク技術」とFSLの「低消費電力プロセス技術」を組み合わせることで、電源電圧0.425VでのSRAM動作に成功したことを発表した。同成果は、12月5日から7日まで米国ワシントンDCで開催される半導体の国際学会「IEDM(International Electron Devices Meeting)2011」にて報告された。

半導体のプロセス微細化により130nmプロセス程度までは電源電圧を低減できたが、それ以降のプロセスでは1V近傍のまま低減されていない。これは、組み込み型SRAMの動作電圧が低減できないことが1つの要因となっている。

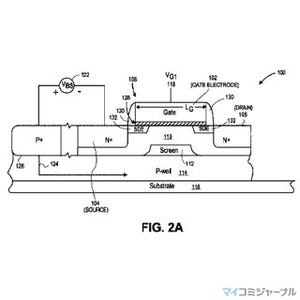

RDF(Random Dopant Fluctuation)を含むいくつかのバラつき要因により、トランジスタのしきい値電圧にバラつきが生じることによるもので、極薄膜SOIトランジスタとフィン型トランジスタ構造で、RDFを改善できるとの報告もあるが、構造的に複雑であり、既存の設計資産や製造資産を利用することが困難と考えられおり、代替的手法が求められていた。

今回、SuVoltaのパワーシュリンク技術の1つであるDDCトランジスタと、FSLの低電力CMOS回路用プロセス技術を用いて製造したDDCトランジスタ構造を用いると、トランジスタのしきい値電圧のバラつきは従来の約半分に低減し、576Kビットの組み込みSRAMで0.425Vの電源電圧での動作確認に成功したという。

この結果は、大半の製品における電源電圧の下限は、組み込みSRAMの安定動作により決まるため、さまざまなCMOS回路を搭載した製品でも0.4V近傍で動作することを実証したことになると両社では説明している。