米SuVoltaは、米ワシントンD.C.で開催されている「2011 International Electron Devices Meeting(IEDM 2011)」において同社の低消費電力トランジスタ技術「Deeply Depleted Channel(DDC)」の詳細を公表した。

DDCは、同社の低消費電力型CMOSプラットフォーム「PowerShrink」を構成する技術であり、動作速度を落とすことなく消費電力を50%削減できるというもので、同社では最新の電圧スケーリング手法とDDC技術を組み合わせることで、消費電力を80%以上削減できると説明している。

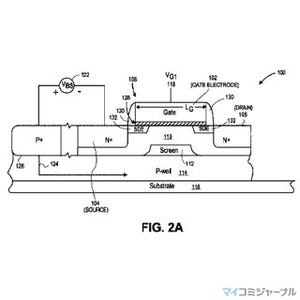

このDDCトランジスタは、しきい電圧(VT)のバラつきを抑え、CMOSプロセスの微細化を押し進めることができる技術だという。具体的にはゲートに電圧を印加すると、チャネル領域の空乏層が基板方向に深く広がっていく仕組みを利用する。DDCチャネル構造は一般に不純物がほとんど含まれない領域と、VTを設定すべきオフセット領域、そしてスクリーニング領域の3つの領域から成り立つとするが、実際は、ウェハプロセス工場やチップ・デザインの要件に応じて異なる可能性があるという。

この不純物がほとんどない領域では、チャネルの不純物が少なくなり、空乏層がチャネルいっぱいに広がるため、RDF(ド―パントのランダムな変動)が小さくなり、VDDをスケーリングできるとともに移動度が向上し有効電流が増加することとなる。

また、VTを設定するためのオフセット領域は、チャネル移動度を劣化させることなくトランジスタのしきい電圧を設定する部分であり、この領域も、従来のトランジスタよりもVTのバラつきが改善されるという効果があるという。

そしてスクリーニング領域は電荷を遮蔽し、空乏層の深さを決める部分だが、この領域を活用すれば、必要に応じて基板バイアスによってVTをダイナミックに調整することも可能となるという。

このため、DDCトランジスタでは、電源電圧を下げることが可能となり、低消費電力動作が実現できるようになり、またVTのバラつきをコントロールすることができるため、 性能を落とすことなく、動作電圧を30%低減できるほか、リーク電流の提言、そして歩留りの改善が可能になるという。

加えて、DDCトランジスタでは、複数のVT設定も可能なため、チャネル移動度を向上させ駆動電流を増加させたり、ドレインによるバリヤのローディング効果(DIBL:Drain Induced Barrier Loading)を小さくできたり、ボディ係数の増大による、VTのコントロール性の向上が可能になったりするという。

なお、同社CTOのScott Thompson氏は、「チップには、これ以上小型化しても意味がない時代がくる。リソグラフィのコストが上昇し、トランジスタ1個あたりの製造コストが横ばいになることで、ムーアの法則が成立しなくなるのではないかと心配する時期が見えてきた。現在、28nmや20nmが用いられようとしているが、このプロセス世代はかなり長く使われるものとなるだろう。マイクロプロセッサは別として、モバイル市場向けのチップにはコスト管理と消費電力の削減が重要となるが、DDCトランジスタは従来からのCMOSプロセスと互換性のある技術であり、低消費電力化を進めつつ既存プロセス技術の延命を図る解の1つとなる」とコメントしている。