Lattice Semiconductorは、低消費電力・低コスト性能を維持しながら高機能を新たに搭載したミドルレンジFPGA「LatticeECP4ファミリ」を発表した。

同社は低消費電力・低コストのFPGAに注力しており、2009年に発表したミドルレンジFPGA「LatticeECP3ファミリ」は市場で高い評価を得ている。今回のECP4はECP3をベースとし、より高いパフォーマンスを実現した製品となっている。

低コスト・低消費電力FPGAを高機能化

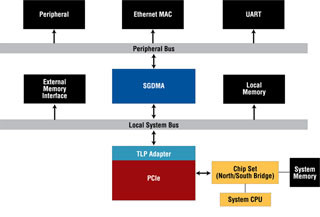

ECP4ファミリは、33K~241K LUTの6品種で構成される。ECP3からの性能向上については、まずプログラマブルファブリックが最大149K LUTから最大250K LUTへと66%増加した。SERDESは3.2Gbpsから6Gbpsへと2倍に高速化し、ファブリックも30%向上している。6Gbps動作時の消費電力はチャネル当たり175W以下となっている。また、組み込み型メモリの容量が42%増、CDR機能対応GIGA sysIOが50%高速化している。さらにMACOコミュニケーション・エンジンはハードIPによりリソース使用効率を10倍向上している。

なお、POWER sysDSPブロックは、500MHz以上まで動作する最大36×36の乗算・アキュミレート機能を備えたDSPブロックで、フィルタの性能とリソース効率を向上している。ECP3に対してはDDRモードに対応するブースターロジックにより2倍、対称係数の信号処理を活用するプリアダーロジックにより2倍、最大576個の乗算器ロジックにより最大1.75倍向上し、最大で7倍のDSP処理性能を実現した。

高効率の成熟技術により低コストを実現

ECP4において低コスト・低消費電力を実現するために、まず成熟した低コスト65nmプロセスを採用した。

製品発表に先立って都内で開催された記者説明会においても、同社シリコン/ソリューションズ マーケティングディレクタのShakeel Peera氏は65nmプロセスの使用のメリットを強調した。ミッドレンジFPGAにおいては小型デバイスにおけるウェハコストや歩留まりなどコスト優位性は28nmプロセスよりも65nmプロセスの方が優れているという。また、ウェハのコストについては、28nmのウェハコストは65nmの2倍となっており、今後も2013年~2015年の時点では28nmのウェハコストは65nmの1.6倍になると見ており、小規模のFPGAであれば、現時点では65nmプロセスの方が合理的であると判断しているとした。

同社では、65nmプロセスのコスト優位性はECP4が大量生産されてからも2016~17年頃までは維持できると見ている。なお、以降のデバイスについては、ファンドリパートナーの富士通セミコンダクターが45nm以降の生産を行わないこともあり、新たなファンドリパートナーと28nmプロセスで展開する可能性を示唆している。

さらにパッケージングでは、フリップチップよりも安いワイヤボンドを採用し、またCDR対応I/Oにより実装コストを低減している。なお、ワイヤボンドパッケージで6G SERDESなどに対応する技術の詳細は明らかにしていない。

デバイスに最適なアーキテクチャにより低消費電力を実現

低消費電力の実現に向けては、低コスト・低消費電力の中規模デバイスに最適化したアーキテクチャを導入した。大容量で高オーバーヘッドのプラットフォームではなく、中規模デバイスに特化したプラットフォームで開発を行い、最適な低消費電力を実現した。

また、ハードマクロ化したMACOコミュニケーション・エンジンの採用により、消費電力を1/10に低減した。さらにロジック対配線の電力比を見直し、従来のFPGAではダイエリアの7割を占めていた配線部を削減した。ダイナミック電力の増加分を抑制しながら、高性能を実現した。一部の競合製品との比較では、250K LUTにおいて28nmプロセス製品よりも消費電力を抑えている。

ECP4は、2012年上期にエンジニアリングサンプル出荷、同年下期に量産出荷を開始する予定。価格は現段階では公表できないとしている。開発ツールについては、一部のユーザーに対して「Lattice Diamond 1.4設計ソフトウェア(ベータ版)」の提供を開始している。